基于折叠结构的半带滤波器的设计

下面以一个基于折叠结构的11阶半带滤波器的设计为例来说明设计的可行性及优越性。

2. 2. 1 设计指标

设计指标:系统时钟为61. 44MHz,半带滤波器的阶数11 阶,系数为定点18 位,滤波器通带要求1. 23M,阻带位置要求为30. 72 - 1. 75 = 28. 97M。

2. 2. 2 下采样数据率变换

半带滤波器作为抽取器使用时,其抽取因子为2,即输出速率为输入速率的一半,也就是说输出速率与系统时钟频率是1: 2的关系。为了采用折叠技术,同时也方便整个滤波过程的时序控制,首先我们利用系统时钟产生一个同步控制信号cONtr_ rw。

同步控制信号contr_ rw的初始值为1,在每个系统时钟上升沿到来时,其值在0与1之间进行跳变,其它时候数值保持不变,也就是说在第一个系统时钟上升沿到来时, contr_ rw的值由1跳变为0,此值一直保持着,直到第二个系统时钟上升沿到来时, contr_rw的值才由0跳变为1,同样此值也一直保持到第三个系统时钟上升沿到来时才发生跳变。由此可见contr_rw的值只有在系统时钟上升沿到来时才发生跳变,为此我们可以用此同步控制信号作为分路器(DEMUX)的选通开关把输入数据分成奇、偶2个通道,以此达到下采样数据率变换。当系统时钟上升沿到来时,如果同步控制信号contr_ rw的值为0,则把输入数据送入奇通道,此时偶通道送入的是0值;如果contr_rw的值为1,则把输入数据送入偶通道,此时奇通道送入的是0值;紧接着在经过两级的数据率稳定之后,奇、偶2个通道的数据率均为系统时钟频率的一半,也就是说此时奇、偶通道均为每两个时钟变化一次数据。根据公式2,我们知道此11阶半带滤波器的输出为:

由此表达式我们知道x ( n) h0、x ( n - 2) h2、x ( n - 4) h4、x (n - 6) h4、x (n - 8) h2、x (n - 10) h0 是根据奇通道数据产生的, x (n - 5) h5 是根据偶通道数据产生的。为了节约资源同时也为后续的折叠技术的应用,系数h2、h4 采用分时复用技术,当同步控制信号contr_rw的值为0时产生系数h4、contr_rw的值为1时产生系数h2。

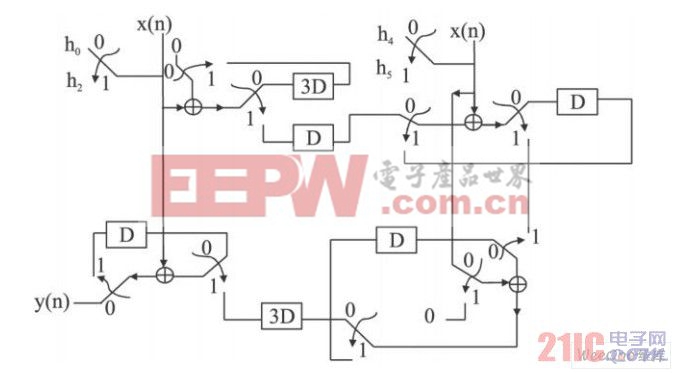

2. 2. 3 各结点延时单元计算

首先我们把设计当中用到的每个乘法器和加法器都当成一个结点,在应用折叠技术之前我们必须先知道各结点之间的延时值。如图1所示我们标注好每个结点的编号,为了让其结构具有对称性,我们把图1当中的结点12当成是一个加法器,此加法器的输入分别为: 0值和结点8的输出值。由于时钟频率是输出速率的2倍,因此折叠因子N = 2, 此时所有编号为奇数的结点其u或者v值均为0,所有编号为偶数的结点其u或者v值均为1,根据公式3我们可以算出各个关键结点之间的延迟值为:DF ( 5→6) = 5、DF (6→7) = 3、DF ( 7→8) = 3、DF ( 8→12) =0、DF (12→11) = 1、DF ( 11→10) = 5、DF ( 10→9) =3。根据这些延迟值,我们知道完成一次的滤波工作需要22个系统时钟和20个D触发器。为了能够以最快的速度完成滤波功能,这时可以引入重定时技术对D触发器进行分配,在满足时序的情况下减少D触发器的使用, 从而减少延迟。重定时后各结点的延迟值为: DF ( 5→6) = 3、DF ( 6→7) = 1、DF ( 7→8) = 1、DF ( 8 →12) = 0、DF ( 12 →11) = 1、DF ( 11 →10) = 3、DF ( 10→9) = 1,也就是说采用重定时以后完成一次的滤波工作只需11个系统时钟和10个D触发器。于是根据这些延迟值我们便得到了折叠结构的结构图,如图2所示。

图2 基于折叠结构的半带滤波器的结构图

评论