基于折叠结构的半带滤波器的设计

2. 2. 4 时序分析

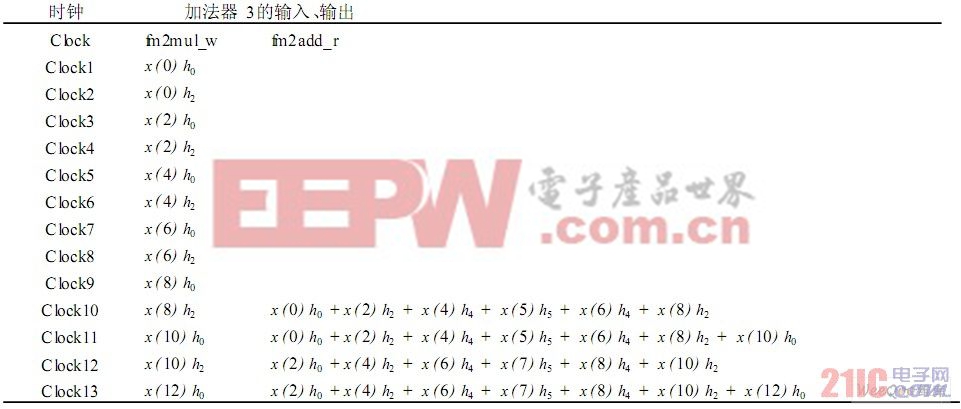

图2当中的0表示同步控制信号contr_rw的值为0, 1表示同步控制信号contr_rw的值为1,为了方便分析,我们把图2当中的加法器按照从左到右,从上到下的顺序依次编号为加法器1、加法器2、加法器3、加法器4,用fm0mul_w表示通道送给加法器1的输入, 用fm0add _ r 表示加法器1 的输出; 用fm1mul_w表示通道送给加法器2的输入,用fm1add_r表示加法器2的输出,其它类推。接下来简要的分析下该设计是如何工作的。

第一个时钟Clock1:同步控制信号contr_ rw的值为0,通道送入加法器1 的数据为x ( 0) h0 , 加法器1的另一个输入值为0,此时加法器1的输出值为x (0) h0 ;通道送入加法器2的数据为x ( 0) h4 ; 通道送入加法器3的数据为x ( 0) h0 ;通道送入加法器4的数据为x (0) h4。

第二个时钟Clock2:同步控制信号contr_ rw的值为1,通道送入加法器1的数据为x (0) h2 ;通道送入加法器2的数据为x (1) h5 ;通道送入加法器3的数据为x (0) h2 ;送入加法器4的数据为0。

第三个时钟Clock3、第四个时钟Clock4、第五个时钟Clock5、第六个时钟Clock6可按照此方法依此类推,具体时序参见表1。

第七个时钟Clock7:同步控制信号contr_ rw的值为0,通道送入加法器1的数据为x (6) h0 ,加法器1的另一个输入值为0, 此时加法器1 的输出值为x (6) h0 ;通道送入加法器2 的数据为x ( 6 ) h4 , 在Clock6产生的fm0add_ r经过1个时钟延时成为此时刻加法器2的另外一个输入值,于是此时加法器2的输出值为x (2) h0 + x (4) h2 + x (6) h4 ;通道送入加法器3的数据为x (6) h0 ;通道送入加法器4的数据为x ( 6) h4 ,在Clock6产生的fm3add_ r经过1个时钟延时成为此时刻加法器4的另外一个输入值,于是此时加法器4的输出值为x ( 0) h0 + x ( 2) h2 +x (4) h4 + x (5) h5 + x (6) h4。

第八个时钟Clock8、第九个时钟Clock9、第十个时钟Clock10 可以按此方法类推, 具体时序参见表1。

第十一个时钟Clock11: 同步控制信号contr_rw的值为0,通道送入加法器1 的数据为x ( 10 )h0 ,加法器1 的另一个输入值为0, 此时加法器1的输出值为x ( 10) h0 ;通道送入加法器2的数据为x ( 10) h4 ,在Clock10产生的fm0add_ r经过1个时钟延时成为此时刻加法器2 的另外一个输入值,于是此时加法器2的输出值为x ( 6) h0 + x ( 8) h2 +x (10) h4 ;通道送入加法器4的数据为x ( 10) h4 ,在Clock10产生的fm3add_r经过1个时钟延时成为此时刻加法器4的另外一个输入值,于是此时加法器4的输出值为x ( 4) h0 + x ( 6) h2 + x ( 8) h4 + x ( 9) h5+ x (10) h4。通道送入加法器3的数据为x ( 10) h0 ,在Clock10产生的fm2add_r经过1个时钟延时成为此时刻加法器3的另外一个输入值,于是此时加法器3的输出值为x ( 0 ) h0 + x ( 2 ) h2 + x ( 4 ) h4 +x (5) h5 + x (6) h4 + x (8) h2 + x (10) h0。

以上是基于折叠结构的11阶半带滤波器一个完整的滤波过程。具体的各个结点的时序如表1所示。

表1 时序表

评论