关于模拟数据采集的设计权衡的分析与研究

模拟采集部分是所有数据采集系统的核心。微处理器、数字信号处理器、存储器、固件、软件驱动、操作系统和软件应用都可能构成一个系统的大脑,但它们实际上还是模拟电路。要针对某种应用建立一个有必要的速度、分辨率和精度的系统,需要寻找模拟数据转换器、运放、复用器和电压基准的正确组合。

图 1 是模数转换器(ADC)中通过基本模拟信号的路径。每个数据采集系统都要使用这种基本配置的某种形式。为每个元件所做的选择会影响到对其他元件的选择。

模拟信号路径开始于输入连接器。多数数据采集系统会在模拟电路前采用某种形式的电路保护。例如保险丝或箝位二极管等元件可以限制进入系统的电压或电流,以保护元器件不会损坏。

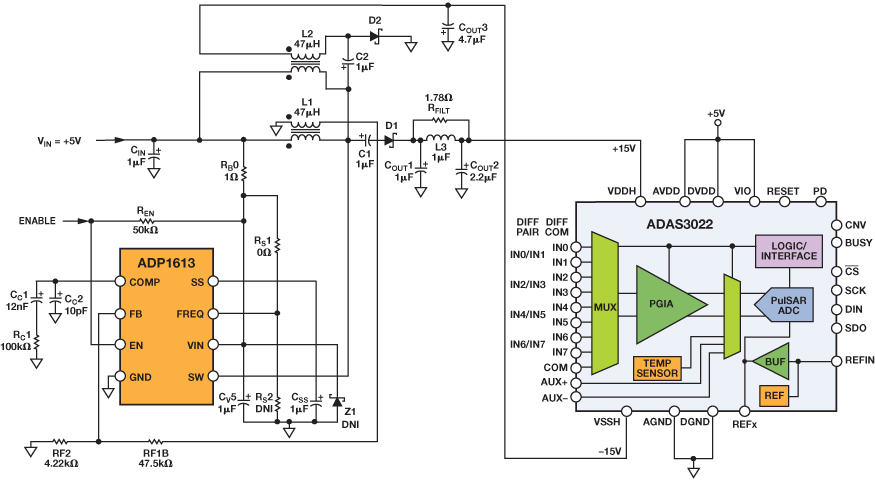

数据采集系统很少采用单一的测量通道。数字万用表(DMM)一般只有一个通道,但可以用继电器与 DMM 结合来增加通道数。数据采集系统(无论是插件板、USB 模块或独立系统)每个通道都可能有一个专用的 ADC,或只有一个 ADC,由复用器(mux)连接到多个通道。每个通道都有专用 ADC 使系统的所有通道可以同时采样。

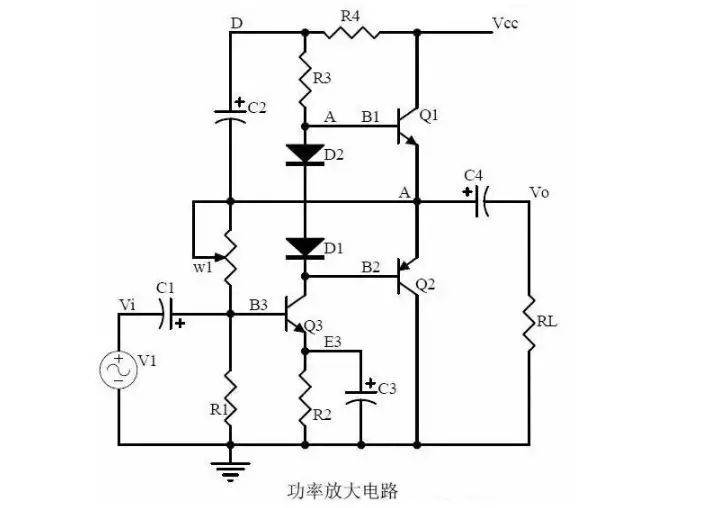

在复用器之后(如果系统使用的话),可编程增益放大器(PGA)对来自传感器或其他信号源的输入电压进行放大或衰减,使之最佳地适配 ADC 的输入电压范围。有些系统可能采用第二只运放,它为输入信号增加了一个 DC 偏置电压。偏置电压用于使信号偏移,使之定位于 ADC 输入范围的中心。因此,ADC 输入电压范围就是选择 PGA 的主要因素。

也可以使用附加的箝位电路来保护 ADC。在 ADC 之前,大多数系统设计者都增会加一个低通抗混叠滤波器。这个滤波器用于限制信号路径的带宽,在 ADC 进行信号数字化以前尽可能减少混叠的最后机会。

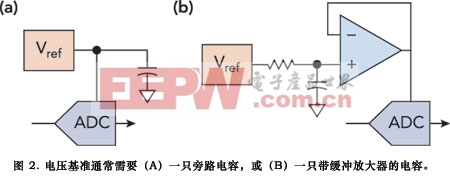

要成功地数字化模拟信号,ADC 需要一个基准电压 Vref。有些 ADC 带有内部基准,而其他则采用外接基准源。

Keithley Instruments 公司的高级总工

程师 Kevin Cawley 说:“我们偏向于外接电压基准。我们认为,外接电压基准要比内置的更稳定。”

United Electronic Industries(UEI)的工程经理 Alex Ivchenko 进一步说:“如果你用外接基准,就可以通过控制 ADC 基准电压来调节输入路径的增益。如果输入电压太高,就需要提供一个更高的 Vref。”

ADC 的数字输出可以是串行方式,也可以是并行方式。串行总线能提供更好的模拟性能,因为在一个给定时间内只有较少的线路需要改变,可以尽量减少在电源与地线上的反跳,并降低了总系统噪声。但是,对于相同的位数,串行接口运行的时钟频率高于并行总线,因此,必须小心地发送信号以减少噪声。

ADC 的选择

ADC 的选择涉及很多必须考虑的设计权衡。数据采集系统中的多数 ADC 都采用逐次逼近型(SAR)或 Σ-Δ架构。一般来说,SAR 器件的速度高于 Σ-Δ ADC,但 Σ-Δ 架构有更高的分辨率。如果需要高于 18 位的分辨率,就需要 Σ-Δ 转换器。

ADC 的采样率与电源电压将决定可以使用的支持电路类型。以电源电压为例,今天的多数 ADC 采用 CMOS 工艺而不是双极工艺制造。CMOS 器件的功耗远低于双极器件,还可以采用较低的电源电压轨运行。双极器件可能需要 12V 或 15V 电压轨,而 CMOS 器件可以采用5V、4V、3.3V、2.5V 甚至 1.8V 的单极电源。

尽管低电压能降低功耗,但它们也压缩了 ADC 的动态范围。ADC 运行在 12V 时,其动态范围是 0-4V 器件的六倍。因此,同样数量的噪声对 12V 系统的影响远小于一个 4V 系统。所以,必须使进入 ADC 的噪声低于 1 个最低有效位(LSB)。ADC 前的运放噪声级要与 1 LSB 动态范围相一致。这意味着24 位 ADC 的噪声要比 16 位ADC 更低。

Cawley 称,为获得更好的动态范围,应该尽可能使高电平信号远离模拟通道。他指出,Keithley 的 DMM 在 10V 范围内可以提供最佳的精度,此时对进入的信号既不需要放大也无需衰减。

评论