Hummingbird加密算法的硬件架构设计

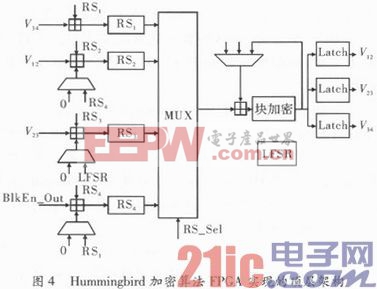

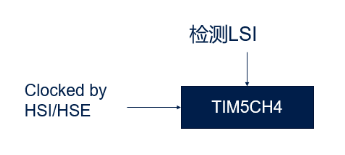

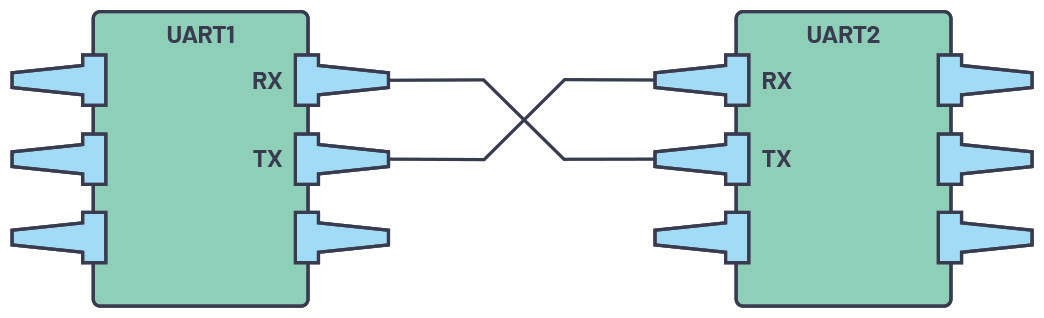

在这一架构中,需要5个异或器、8个S—Box、一个线性变换过程及两个多路选择器。Hummingbird加密算法FPGA架构的顶层设计如图4所示。本文引用地址://m.amcfsurvey.com/article/189549.htm

在顶层架构中,块加密的输出首先被锁存器锁存,在初始化和每轮的加密过程反馈,以便更新状态寄存器。由于初始状态和每轮加密的状态寄存器更新机制不同,因此需要数据选择器来实现正确的更新,更新后的状态寄存器在每轮加密过程中,分别输入至块加密过程。同时,由于初始化过程需要随机数产生,因此,使用LFSR来实现,以便节省硬件资源。

3 结果分析

文中使用Xilinx FPGA Spartan-3平台,利用VetilogHDL来实现所提出的硬件架构。将所提出的架构和其他设计进行比较。文献第一次提出了Hummingbird加密算法的FPGA实现架构,但其所需的硬件资源较多。文献提出的方法虽然花费得硬件资源少,但速度较慢,同时需要更多的存储器,实际所需的硬件资源并未减少。同时,文献使用的是协处理器方法,并不能算作是硬件架构。

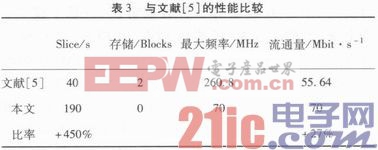

在表2中,给出了本次的方法和文献的性能比较。

表2所示,提出方法所需的硬件资源比文献少25%,同时速度也提升了6%。而在表3中,给出了文中的方法和文献的性能比较。

相比于文献,提出方法虽然所需的Slices数量较多,却无需存储器,同时速度可提升约30%。

4 结束语

文中提出了一种有效针对Hummingbird加密算法的FPGA硬件实现。该硬件架构相比其他方法可使用更少的硬件资源,同时速度上也优于其他方法。因此该架构可广泛用于RFID等硬件资源受限的加密平台中。

评论