YUV分离的两种FPGA实现

2 基于面积的实现

面积通常可以通过一个工程运行所消耗的触发器(FF)和查找表(LUT)数量已经等效门数量来衡量,即所消耗的资源来衡量。本文基于面积的设计,充分考虑到用户对集成度和智能化的要求。对于集成度和智能化的提高,应该着眼于每一部分的优化,才能获得整个系统集成度和智能化的提高,因此,本文对YUV分离这个模块进行了研究优化。本文引用地址://m.amcfsurvey.com/article/190540.htm

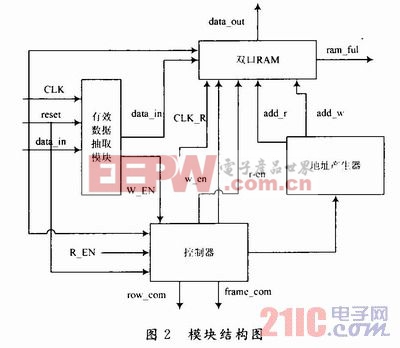

该模块基于面积的设计采用一片双口RAM进行模块结构图如图2所示。有效数据抽取模块与控制器和双口RAM的输入时钟应与FPGA工作时钟保持一致。有效数据抽取为双口RAM提供写使能,每行提供的有效视频数据为704个像素,等到该模块检测到有效视频数据的时候,对双口RAM发出读使能,然后接下来利用704个CLK完成对双口RAM的写操作,等到写完毕时向SDRAM发出满信号,在SDRAM收到该信号后,产生读使能,以便对双口RAM构成的读操作。该模块的设计思想是基于FPGA与SDRAM频率差异进行设计的。一帧视频数据由625行视频组成,分奇、偶两场,每一帧都是由有效视频数据和场消隐数据组成的。其中23~310和336~623为有效视频数据,共576行。其余49行为场消隐数据,每一行同样分为行有效数据和行消隐数据。如果FPGA的工作频率与SDRAM的频率满足一定的差异(本文采用的FPGA频率为48 MHz,而SDRAM采用100 MHz的时钟频率),那么在一行视频数据的有效期完成对双口RAM的写入后,在该行视频数据的行消隐期内,可以通过输入100 MHz的时钟来完成对双口RAM的读操作。该模块完成对有效视频数据的写入需要1 408个CLK,而完成存储数据的读取需要704个CLK_R,所需时间为1 408×10-8+704×(1/48000000)。因为读/写是串行执行的,故以后每一行有效视频的写入/读出均需要相同的时间,一行数据读出完毕的仿真如图3所示。

电子镇流器相关文章:电子镇流器工作原理

评论