YUV分离的两种FPGA实现

3 基于速度的实现

前面提到了FPGA设计中面积与速度不断变换的原则,基于面积的实现方式只用到了一片双口RAM,在一定程度上达到了面积优化的目标,但是也看到读/写是串行执行的,在系统运行速度上确实有一定的缺陷,无法满足系统对实时性的要求,同时系统需要两个不同频率的时钟,容易引起亚稳态。下面将介绍一种基于速度的实现方式。

3.1 乒乓操作

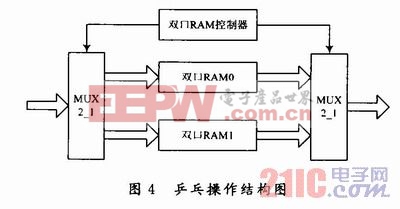

乒乓操作是一个用于数据流控制的处理技巧,本文利用了两片双口RAM来作为乒乓操作的数据缓冲区,乒乓操作如图4所示。外部视频数据在输入数据选择控制模块和输出数据选择控制模块的控制下,完成缓冲区的选择和视频数据的输入/输出,并将经过缓冲的数据流不停顿地送到下一模块进行运算或处理。它适合于对数据流进行流水线式处理,能高效地完成大量实时视频数据的无缝缓冲和处理。在第一个缓存周期,也称之为双口RAM0的写周期。视频数据在双口RAM控制器控制下选择将视频数据输入到双口RAM0;在下一个周期,输入控制模块将视频数据输入到双口RAM1,同时输出控制模块输出双口RAM0的视频数据到后续模块进行处理;在第三个周期时,在输入控制模块的控制下,将输入视频数据输入到双口RAM0,同时在输出控制模块控制下,将双口RAM1中存储数据输出到后续模块,如此不断循环。本文引用地址://m.amcfsurvey.com/article/190540.htm

3.2 模块设计与仿真

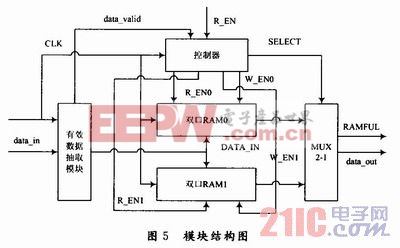

该模块利用了两片双口RAM在不同的缓冲周期内分别进行读/写。该模块主要由有效数据抽取、双口RAM控制器、两片双口RAM组成,模块结构如图5所示。该模块在控制器控制下视频数据经有效数据抽取模块抽取后进入双口RAM,控制器为双口RAM提供读/写使能,通过写使能控制数据写入是否有效,data_valid是有效数据抽取模块,用来标识有效视频数据的信号,由它为模块提供写使能,等到写操作完成后向SDR AM控制器发送满信号,此时读使能r_en由SDRAM控制器提供。通过控制器提供的读/写使能完成两片双口RAM的读写切换。该模块利用了两片双口RAM之间的乒乓操作,流水地实现了YUV分离的并行处理。

电子镇流器相关文章:电子镇流器工作原理

评论