基于FPGA的LVDS接口应用

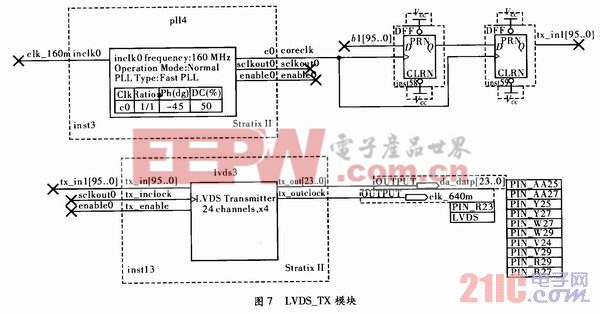

LVDS_TX模块的设置如图7所示,这里使用外部时钟控制,即在LVDS模块外重新定制一个PLL,此PLL要设置在LVDS模式下,PLL类型会自动选择为Fast PLL。这时PLL会有3个输出c0,sclkout0,enable0。输入时钟inclk0设为160 MHz,LVDS数据率置为640 Mbit·s-1,则输出c0为核时钟,频率为160 MHz,输出sclkout0为串行化输出时钟640 MHz,输出enable0为LVDS输入使能信号。本文引用地址://m.amcfsurvey.com/article/190723.htm

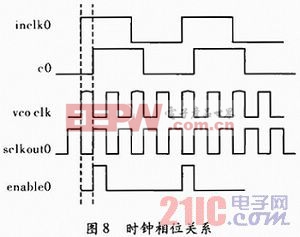

在外部PLL设置中可以对输出的核时钟和高速串行化输出时钟的相位进行调节,因为FPGA的高速时钟由于内部布线等原因可能会产生一些相位偏斜,导致数据和时钟不能准确对齐,这时就需要对时钟的相位进行调节来对齐数据和时钟。本实验中设置c0的相偏为-45°,则sclkout0会默认产生-180°相偏,因为LVDS设置的是4倍抽取关系,即45×4=180,使用外部时钟时还可以根据需要分别调节两个时钟的相位。时钟相位关系如图8所示。

用PLL输出的核时钟即c0将rearrange模块输出的数据进行同步后送至LVDS_TX模块,时钟的连接方法如图7所示。在enable0信号有效时将数据输入至LVDS模块,LVDS_TX模块输出的24位数据输入给2个DA(I、Q),低12位为I路,高12位为Q路,并将输出640 MHz同步时钟送至DA。此时LVDS模块内仍可以调节输出数据和输出时钟的相位,但只剩下2个相位值可以调节,即0°和180°。

4 实验结果及分析

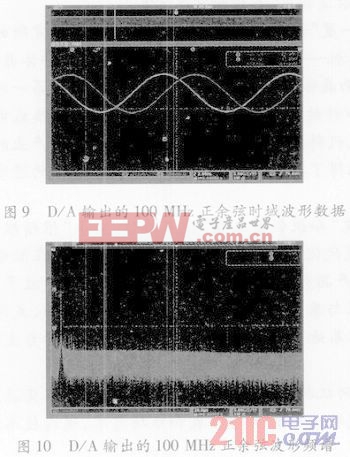

实验中由DSP分别发送100 MHz和225 MHz的正余弦波形数据至FPGA,经过双口RAM和LVDS_TX模块发送至AD9735,并从示波器上观察DA的输出波形。

实验中c0相偏为-45°,sclkout0为-180°相偏。由DSP首先发送的是100 MHz的I、Q波形数据,AD9735的输出波形在示波器上显示如图9所示,其频谱如图10所示。

在100 MHz时,其杂散抑制可达-41.6 dB。

fpga相关文章:fpga是什么

评论