解读FinFET存储器的设计挑战以及测试和修复方法

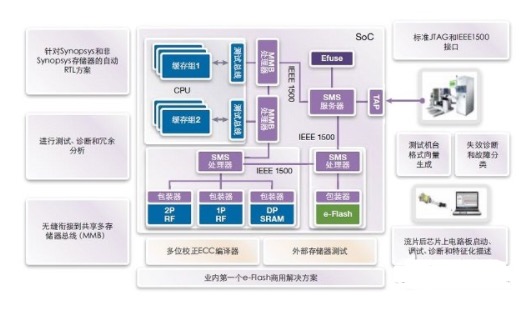

图4:DesignWare STAR存储器系统:针对制程优化了的存储器测试、修复诊断

每个STAR存储器系统处理器的能力都足以处理芯片上的检测、诊断和缺陷修复。连接和配置所有紫色方框可能比较耗时且容易出错,所以STAR存储器系统还实现了以下工作的自动化:

生成、插入和确认配置

完成测试向量的生成

执行故障分类

定位失效

纠错(如果可能)

Synopsys将所有这些自动化步骤映射在FinFET工艺上,以便处理与FinFET存储器有关的新的分类和失效问题。

自2012年起,Synopsys就一直与产业生态系统中得以较早接触制程参数的存储器设计人员合作。在多个FinFET厂家的配合下,Synopsys分析了他们的位单元,也检查、验证了他们的模型,创建测试芯片并在Synopsys内部实验室中直接对硅芯片进行了分析。这个过程让Synopsys加深了对FinFET缺陷问题的认识,使Synopsys可以优化STAR存储器系统来解决它们。

因此,如今STAR存储器系统已被使用在多个方面:

工艺开发:利用STAR存储器系统特征化描述和理解晶圆制造工艺

IP鉴定:特征化描述和鉴定存储器IP本身

SoC设计:将STAR存储器系统纳入SoC设计分析中,包括生产测试和修复

管理现场可靠性和老化:处理FinFET工艺中固有的、与鳍片突出和底层热隔离有关的热问题。SoC寿命中出现的问题可能是小到软性错误的小问题,它们可以通过纠错代码(ECC)自动纠正。但是高可靠性系统中的老化可能需要定期或在上电时使用STAR存储器系统修复生产测试完成很久以后在现场出现的故障。

当然,存储器并非芯片上唯一需要测试的部分。还有逻辑模块、接口IP模块、模拟混合信号(AMS)模块等(也需要测试)。Synopsys提供了一组能与STAR存储器系统平滑整合的全面的测试和IP方案(图5)。对于逻辑模块,Synopsys提供的是DFTMAX?和TetraMax?。接口IP(如DDR、USB和PCIe)有自己的自测试引擎,但它们都能无缝地配合STAR层次化系统(Synopsys的系统级测试方案)一起工作。仅有针对单个模块的解决方案是不够的,SoC必须流畅地在顶层上工作。

图5:Synopsys测试和良率解决方案:提高质量、可靠性和良率

认识FinFET存储器故障和缺陷

理解如何测试和修复存储器之前,设计人员需搞清楚存储器失效的方式。比如,电阻性故障显现出来的是逻辑上的性能问题,虽然逻辑通过了测试但无法全速工作。在存储器中,电阻性故障可以表现为更加微妙的方式。这种故障可能只有在多次操作(一次写入操作后接着几次读操作)之后才引起可检测性的错误,而不是在更标准的一次操作(一次读操作)后。

设计人员还必须通过研究布局确定哪些错误可能真正发生。在数字逻辑测试中,可以通过分析哪些金属是相邻的而且可能短路来大幅提高覆盖率。在存储器中通过分析信号线可能出现失效等问题所在位置的潜在电阻性短路亦可做到这点。这需要综合研究布局和分析测试芯片,发现可能的故障。深度分析的需求是Synopsys在多家代工厂中运行50多个FinFET测试芯片的理由之一。来自这些测试的信息用于改进STAR存储器系统。

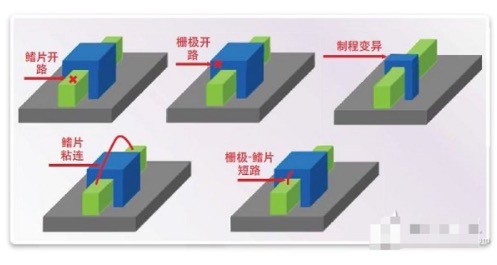

图6表明了FinFET工艺可能存在的几种不同的缺陷类型。图中每个晶体管只有一个鳍片,而实际上每个晶体管的鳍片通常不止一个。当然,开路和短路都可能发生,但在FinFET中它们可能产生不同的表现:鳍片开路、栅极开路、鳍片粘连、栅极-鳍片短路等。每种情形都可能是硬开路或短路,也可能是电阻性的,其中高低不等的电阻值产生不同的表现。

图6:潜在FinFET缺陷类型

分析布局后,设计人员必须研究拓扑结构,根据晶体管的物理结构判断故障是否真的会发生。

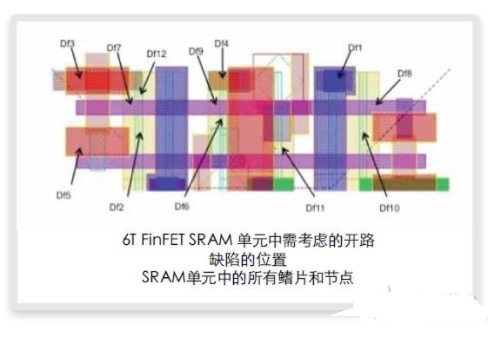

下一步对设计人员来说要从纯晶体管上升一个层级。一个SRAM单元包含六个晶体管,所以要分析这个单元在内部节点中的开路、可能发生的方式以及会产生什么结果。

下一个层次上的目标是单元布局。比如,图7表示六个晶体管SRAM单元中可能发生的所有可能的开路缺陷。第三,设计人员分析整个存储器阵列的故障,如位线中的开路、字线之间的短路等等。最后,在模块级上,整个存储器,包括周围的模块(如地址解码器)都需要检验,就如同读出放大器那样。

实际分析通过缺陷注入继续进行。这基于GDS(版图)本身。缺陷注入在版图和SPICE模型上进行,使用了针对每个库的缺陷库,然后观察它们会如何表现。缺陷注入在所有14/16nm FinFET提供商的晶体管上进行,不论是IDM还是代工厂。缺陷注入也在较高节点(如45nm和28nm)的平面工艺上进行。

图7:FinFET存储器单元版图中注入的开路缺陷实例

缺陷注入展示了每种缺陷的行为方式。接下来的任务就是通过测试序列识别(

评论