这项源自北大 20 年前提出的技术,国际巨头竞相追逐

随着代工厂开发越来越先进的工艺节点以满足消费者的需求,当今先进处理器上的晶体管数量达到数百亿,这与 1970 年代中期只有几千个晶体管的处理器相去甚远。

本文引用地址://m.amcfsurvey.com/article/202401/454642.htm过去几十年中,影响半导体行业最深远的技术就是晶体管的稳步发展。在半导体制造领域,每一代新技术都会带来晶体管密度的提高,近几年,我们也一直能够听到:「摩尔定律无法延续,晶体管无穷小的极限即将到来。」之类的声音。

在最近的 IEEE 国际电子设备会议上,英特尔、三星、台积电三个巨头都展示了自家最新的技术情况。其中,不约而同的出现了CFETS(互补场效应晶体管)的身影。可以说,CFET已经被纳入了芯片路线图的下一步的发展规划。本文,我们将来看看最新的三大巨头披露的最新CFET进展,以及 CFET 令人疯狂的原因。

走向 CFET,走向垂直化

在半导体制造领域,每一代新技术都会带来晶体管密度的提高。但是,这并不是通过减小特征尺寸来实现的,而是通过减少每个晶体管特征数量来实现的。当晶体管无法变得更小时,唯一的方向就是向上。

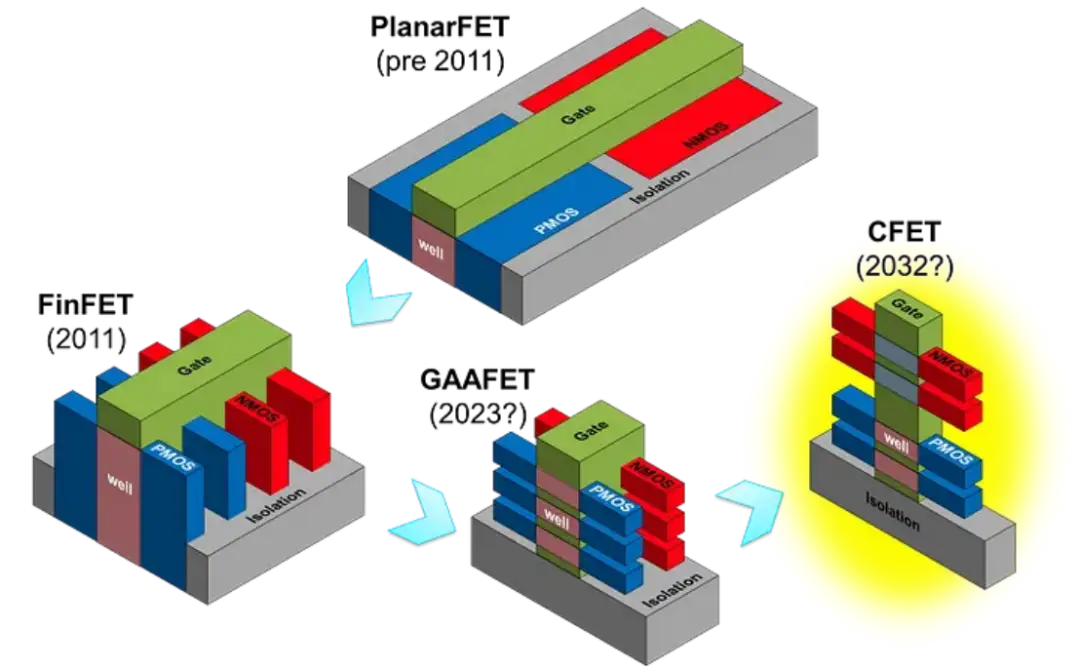

要了解 CFET 解决了什么问题,首先来看看晶体管的演变历程。

在晶体管出现的最早期,传统的晶体管是平面晶体管(Planar FET),这是将栅电极放置在沟道区的顶部来形成的,从而有效地使器件在二维平面中导电。但是,在栅长小于 20nm 的情况下,源极和漏极过于接近且氧化物也愈薄,这很有可能会漏电现象,晶体管尺寸难以进一步缩小。

在 2011 年,英特尔站出来了。率先在 22nm 的技术节点上使用 FinFET(鳍式场效应晶体管)。FinFET 实现了两个突破,第一把晶体做薄并且解决漏电问题,第二向上发展,晶片内构从水平变成垂直。

CMOS 的演变

从上图可以看到,从 Planar FET 到 FinFET,晶体管被「竖」起来了。这一结构的改变非常有效果,在与上一代平面架构相同的性能水平下,功耗降低了约 50%,性能提升了 37%。

半导体工艺持续前进,FinFET 在被提出后也按照摩尔定律预期地提高性能、减小面积。不过,到了 7nm、5nm FinFET 走得已经力不从心了。在 5nm,即使使用了 EUV 光刻机技术,基于 FinFET 结构进行芯片尺寸的缩小稀疏也越发困难。

之后,业内提出 GAAFET(环绕栅极场效应晶体管),这同样也是一个向上发展的方向。本质上来说,GAAFET 就是 FinFET 的鳍片转 90°,再向上堆高,来增加栅极和沟道的接触面积。

GAAFET 的出现,使得晶体管又能向前发展了几代。但还是会有问题,因为 GAA 晶体管架构的能力有其局限性,单个器件的结构形式优化已经几乎推至极限。

这时候 CFET 出场了,继续向上发展。在 CFET 架构中,n 和 pMOS 器件相互堆叠,直接传统 N/P-FET 共平面布局间距的尺寸限制,可以将成电路中逻辑标准单元尺度微缩到 4-T(Track)高度,同时将减少 SRAM 单元面积 40% 以上。

在 1nm 之后,CFET 成为了 GAA 的继任者。今年,英特尔、台积电、三星都先后展示了自家的 CFET 技术,但这项技术在 20 年前,北京大学张盛东博士就已经提出了堆叠互补晶体管(stacked CMOS)概念,并在 2004 年开发完成堆叠晶体管的雏形。

张盛东博士还以一作身份在 IEEE Electron Device Letters ( Volume: 25, Issue: 9, September 2004,P661-663)发表了论文《A stacked CMOS technology on SOI substrate》。

这一论文在英特尔、台积电的相关报告中均被引用。台积电在 VLSI 2021 的报告《CMOS Device Technology for the Next Decade》中指出,北京大学的 3D Stacked CMOS 晶体管是业界第一个堆叠互补晶体管,比台积电和英特尔要早 15 年。

CFET 的神秘面纱?

如前所述,CFET 架构必须垂直堆叠 nMOS 与 pMOS,这就使得制程会更加复杂。目前 CFET 的实现方式业内有两种方案:单片式和顺序式。

单片式 CFET 流程分为三个部分:底部沟道的外延生长、中间层的沉积以及顶部沟道的外延生长。单片式的好处在于,引入 CFET 速度快,与现有的纳米片型工艺流程相比,这种集成方案的破坏性最小,并且成本比较低。

顺序式就是从底部向上制造元件,利用晶圆键合技术,在顶部覆盖一层半导体层,对顶部元件进行集成,并连接顶栅和底栅。顺序式虽然整合的流程相对简单,但是晶圆转移难度高。所以这二者选哪种方式,目前业内还没有明确的定论。

目前国际上在从事 CFET 研究的机构也包括 imec。Imec 的制造蓝图显示,FinFET 晶体管将于 3 纳米达尽头,然后转换到 Gate All Around (GAA) 技术电晶体,2024 年进入量产,之后还有 FSFET 和 CFET 等。

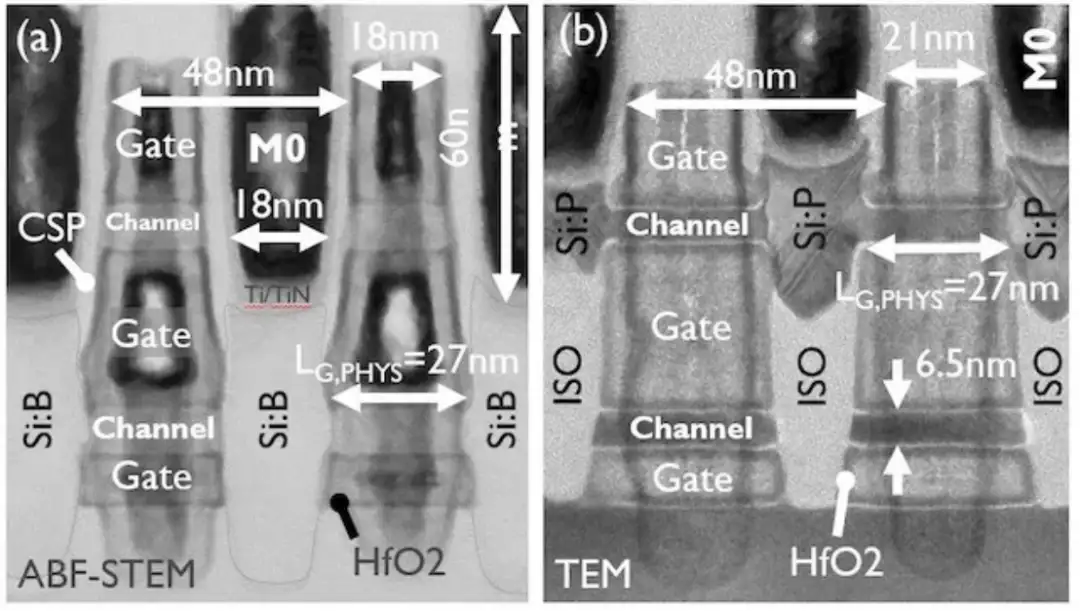

Imec 在 2020 年展示了 CFET 器件,其栅极间距(即接触式多晶间距 (CPP))为 90nm,到了 2023 年,Imec 又展示了通过单片集成以行业相关的 48 nm 栅极间距构建的单极 CFET 器件。

(a) 底部 pFET 和 (b) 顶部 nFET (LG,PHYS=27nm) 的工艺结束横截面 来源:imec

三大巨头 CFET 之争

讲了这么多,我们来看看台积电、英特尔、三星的 CFET 细节。

台积电早在多个技术研讨会上都透露了关于 CFET 的消息,并且表示实验室内部已经拥有可用的 CFET。

最近,台积电发布的最新论文标题为《用于未来逻辑技术扩展的 48nm 栅极间距的互补场效应晶体管(CFET)演示》,再次展示了其对于 CFET 的关注度。

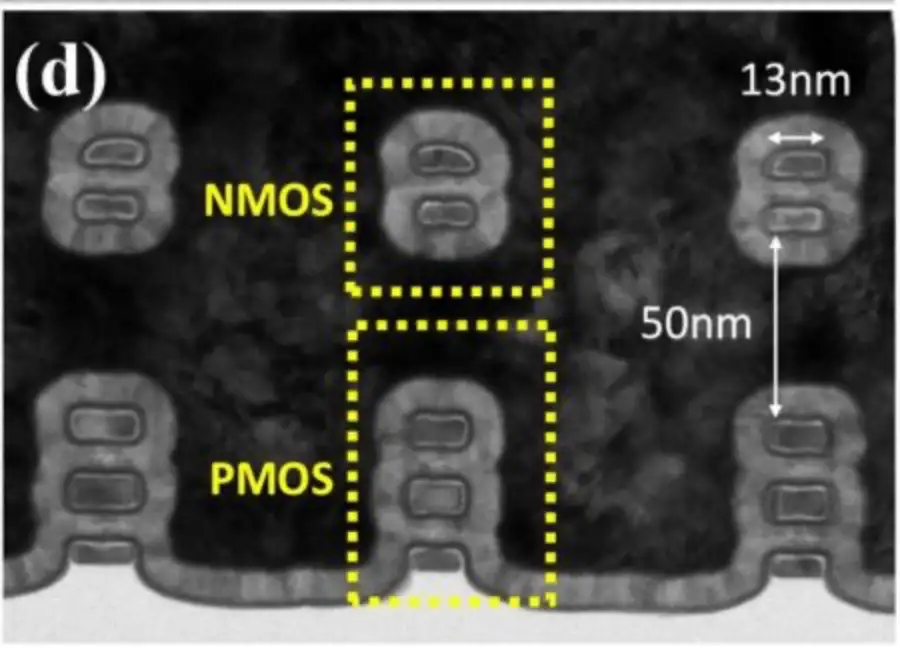

台积电团队将讨论他们所描述的一种实用的单片 CFET 方法,用于在 48 nm 栅极间距上进行逻辑技术缩放。与英特尔一样,他们在 p 型纳米片晶体管之上采用了 n 型纳米片晶体管。该论文将报告通态电流和亚阈值泄漏——在论文概要中分别描述为「高」和「低」。这导致开/关电流比达到六个数量级。

台积电 CFET 联横截面透射电子显微照片显示了台积电的单片 CFET,栅极间距为 48 nm,nFET 放置在 pFET 上方,两种类型的晶体管都被单个金属栅极包围。来源:IEDM

根据论文摘要,晶体管的 FET 良率超过 90%,且成功通过测试。概要中的最后评论是:「虽然仍必须集成其他基本功能才能释放 CFET 技术的潜力,但这项工作为实现这一目标铺平了道路。」

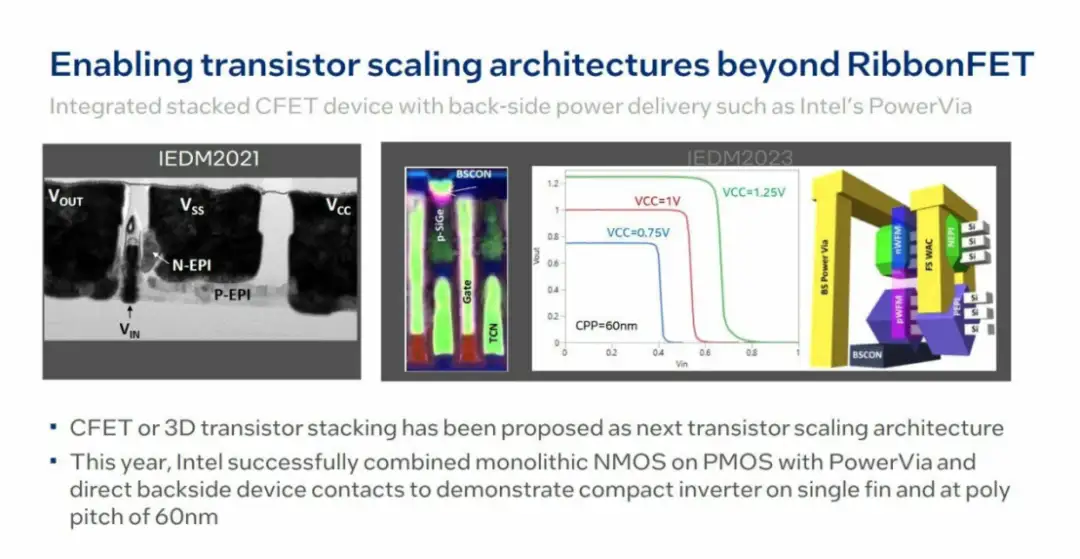

英特尔是三家公司中最早展示 CFET 的,在 2020 年的时候就展示了早期版本的 CFET。同样是 p 沟道和 n 沟道晶体管相互堆叠,以减少 CMOS 对的占用空间。

英特尔堆叠纳米带晶体管的横截面,2020 年

在当年的研究中,这个组合晶体管可提供小于 75mV/十倍频程的亚阈值斜率,以及对于长度超过 30nm 的栅极,漏极感应势垒降低系数小于 30mV/V。尽管这项工作中的门相对较大,但英特尔团队预计通过自对准堆叠可以显著减小单元尺寸。

在今年 5 月,英特尔公布的技术关键路线图中,再次出现了「堆叠式 CFET 场效应管架构」的身影。在其展示的图片中,CFET 设计可以允许堆叠八个纳米片,与 RibbonFET 一起使用,从而增加晶体管密度。

最近,英特尔展示了使用 CFET 制造的最简单电路之一,就是针对反相器的几项改进。CMOS 反相器将相同的输入电压发送到堆叠中两个设备的栅,并产生一个逻辑上与输入相反的输出,而且反相器在一个鳍上完成。英特尔将其描述为:业界首创的 CFET 中功能齐全的逆变器测试电路,采用 60 纳米栅极间距构建。

这次展示的晶体管有三大特点:第一,更密集的电路。60 nm 栅极间距,这表明设计高度紧凑,能够创建更密集的电路。第二,垂直堆叠。采用垂直堆叠双源极/漏极外延,提高了空间效率。此外,它还采用双金属功函数栅极堆叠。这种垂直堆叠最大限度地减少了互连延迟并提高了整体效率。第三,背面电力传输。晶体管采用直接器件接触的背面电力传输对器件的性能和散热有显著贡献。

三星将其 CFET 称为「3DSFET」或 3D 堆叠 FET。目前,三星 3DSFET 结构已被选定为下一代 GAA 技术,并已开始全面商业化的研发。

三星的最新结果和台积电一样,也设法将栅极间距控制在 48nm,其 CFET 解决方案的特点包括一种在顶部和底部电晶体之间形成介电层的新方法,以保持间距。三星使用了一种及湿化学品的新型干刻蚀,取代传统的湿法刻蚀,其成功的解决了电气隔离堆叠的 n 型和 p 型 MOS 元件的源漏电问题。

结语

CFET 是一个具革命性的器件,有可能成为 CMOS 按比例缩小的终极器件。不过 CFET 技术研究仅仅是开始,在准备就绪之前仍有大量工作要做。

业内已经使用 FinFET 五个世代,超过 10 年,而后 GAA 到来了。那么下一代 GAAFET 可能也会应用数年,至少会发展几代。正如台积电表示,新的 CFET 晶体管需要几代人的时间去实现。

评论