如何构建比英伟达更好的GPU

虽然很多人关注各种计算引擎的浮点和整数处理架构,但研究人员却花费越来越多的时间研究内存层次结构和互连层次结构。这是因为计算很容易,而数据移动和存储却变得越来越困难。

本文引用地址://m.amcfsurvey.com/article/202404/457235.htm用一些简单的数字来说明这一点:在过去的二十年中,CPU 和GPU的计算能力增加了 90,000 倍,但 DRAM 内存带宽仅增加了 30 倍,互连带宽也仅增加了 30 倍。近年来,该行业在某些方面取得了进步,但计算与内存的平衡仍然很遥远,这意味着在用于大量 AI 和 HPC 工作负载的内存不足的计算引擎上花费过多。

正是考虑到这一点,研究人员考虑了 Eliyan 创建的网络中物理层 (PHY) 的架构创新,这些创新在本周的 MemCon 2024 会议上以不同且非常有用的方式展现。联合创始人兼首席执行官 Ramin Farjadrad 花了一些时间向大家展示 NuLink PHY 及其用例如何随着时间的推移而发展,以及如何使用它们来构建比使用 PHY 更好、更便宜、更强大的计算引擎当前基于硅中介层的封装技术。

PHY 是一种物理网络传输设备,它将交换芯片、网络接口或计算引擎上或内部的任何数量的其他类型的接口链接到物理介质(铜线、光纤、无线电信号),而物理介质又连接它们相互之间或网络上。

硅中介层是一种特殊的电路桥,用于将 HBM 堆叠式 DRAM 内存连接到计算引擎,例如GPU和定制 ASIC,这些引擎通常用于 HPC 和 AI 领域的带宽敏感应用。有时 HBM 使用也需要高带宽内存的常规 CPU。

Eliyan 于 2021 年在圣何塞成立,目前拥有 60 名员工。该公司刚刚获得了 6000 万美元的第二轮融资,由内存制造商三星和 Tiger Global Capital 领投 B 轮融资。Eliyan 于 2022 年 11 月在 A 轮融资中筹集了 4000 万美元,由 Tracker Capital Management 领投,Celesta Capital、英特尔、Marvell 和内存制造商美光科技 (Micron Technology) 出资。

Farjadrad 在互联网热潮期间在 Sun Microsystems 和 LSI Logic 担任设计工程师,曾担任 Velio Communications(现为 LSI Logic 的一部分)的交换机 ASIC 首席工程师和联合创始人,并且是联合创始人和首席技术 Aquantia 的官员,该公司为汽车市场生产以太网 PHY。2019 年 9 月,Marvell 收购了 Aquantia,并让 Farjadrad 负责网络和汽车 PHY。Marvell 已成为最大的 PHY 制造商之一,在设计这些系统关键组件方面与 Broadcom、Alphawave Semi、Nvidia、Intel、Synopsis、Cadence 以及现在的 Eliyan 等公司竞争。

Eliyan 的其他联合创始人包括 Syrus Ziai,他是工程和运营主管,并曾担任高通公司 Ikanos 的工程副总裁。多年来,PsiQuantum 和 Nuvia 以及业务和企业发展主管 Patrick Soheili 曾负责 eSilicon 的产品管理和人工智能战略主管。该公司因在 Apple iPod 音乐播放器中创建 ASIC 以及开发 2.5D ASIC 封装和 HBM 内存控制器而闻名。当然,eSilicon 于 2019 年底被 Inphi 以 2.13 亿美元收购,扩大了其 PHY 能力,2021 年 4 月,Marvell 在 2020 年 10 月以 100 亿美元收购 Inphi,完成了这一循环。

PHY 以及 I/O SerDes 和重定时器都有资金。SerDes 与交换机 ASIC 中使用的那些用于将从设备发出的并行数据转换为通过电线、光纤或空中传输的串行数据一样,是一种特殊的 PHY,并且从某种思维方式来看,SerDes 也是一种特殊的 PHY。随着带宽的增加以及可以推送干净信号的铜线长度的减少,重定时器将越来越多地被使用。

接下来,一起谈谈 2.5D 封装。

2.5D 封装

随着摩尔定律在晶体管密度方面的增长速度放缓,并且晶体管的成本随着每一种后续工艺技术的发展而不是下降,我们都已经意识到现代芯片蚀刻工艺的掩模版限制。使用普通极紫外 (EUV) 水浸光刻技术,可以在硅晶圆上蚀刻晶体管的最大尺寸为 26 毫米*33 毫米。

许多人可能没有意识到,这也是硅中介层尺寸的限制,硅中介层允许小芯片在有机基板顶部相互链接,有机基板就像每个计算引擎插槽及其附属 HBM 内存下方的主板。该硅中介层的尺寸取决于用于创建中间板的技术。中介层采用与芯片相同的光刻工艺制造,但如今使用一些技术,中介层可以达到 2,500 mm 2,而不是像芯片那样具有 858 mm 2 的掩模版限制,并使用其他接近 1,900 mm 2 ;据 Farjadrad 称,计划将其提高到 3,300 mm 2。有机基板插座没有这样的面积限制。当您谈论小芯片的 2.5D 封装时,这一点很重要。

Farjadrad 向大家介绍了与 Eliyan 的 NuLink PHY 竞争的不同 2.5D 方法的馈送、速度和局限性。

以下是台积电如何通过硅片晶圆芯片 (CoWoS) 工艺实现 2.5D,该工艺用于创建 Nvidia 和 AMDGPU及其 HBM 堆栈等:

从技术上讲,上图显示了台积电的 CoWoS-R 内插器技术,该技术通常用于将 GPU、CPU 和其他加速器链接到 HBM 内存。CoWoS 的硅中介层仅限于大约两个标线单元,这正是 Nvidia 上周刚刚推出的「Blackwell」B100 和 B200 GPU 的尺寸。这并非巧合。这已经是英伟达所能做到的最大规模了。

台积电拥有一种不那么引人注目的 CoWoS-L 技术,该技术制造起来更加复杂,就像其他方法中使用的嵌入式桥一样。

一种桥接技术称为带有嵌入式桥接的晶圆级扇出技术,该技术由芯片封装商 Amkor Technology 倡导,并有来自 ASE Holdings 的一种名为 FOCoS-B 的变体。以下是这种封装方法的速度:

高迹线密度意味着您可以以低功耗获得高芯片间带宽,但范围有限,布线能力也有限。

英特尔将硅桥直接放入容纳小芯片的有机基板中(减去中介层)的方法与 Eliyan 对 NuLink 所做的类似:

然而,EMIB 受到生产周期长、产量低、覆盖范围和可布线性有限等问题的困扰。

这样就剩下了 Eliyan 提出的修改后的 2D MCM 流程 NuLink:

Farjadrad 说,NuLink 是一种 PHY,其数据速率约为传统 MCM 封装的 10 倍,NuLink PHY 之间的走线长度可以达到 2 厘米至 3 厘米,这比 CoWoS 和其他 2.5D 封装选项支持的 0.1 毫米走线长度增加了 20 倍至 30 倍。正如你所看到的,走线上的额外距离,以及 NuLink PHY 在这些走线上具有双向信令的事实,使计算引擎设计变得与众不同。

在当前的架构中,当你在内存和 ASIC 之间运行数据包时,数据包数据不是同时双向的,我们需要自己的特殊协议来维护内存一致性,确保读取和写入之间没有冲突。我们知道当我们制作一个 PHY 时,我们需要为特定的应用制作一个相关的协议。这是我们最大的区别之一。拥有最好的 PHY 是一回事,但将其与 AI 应用的正确专业知识相结合是另一个重要因素,我们知道如何做到这一点。

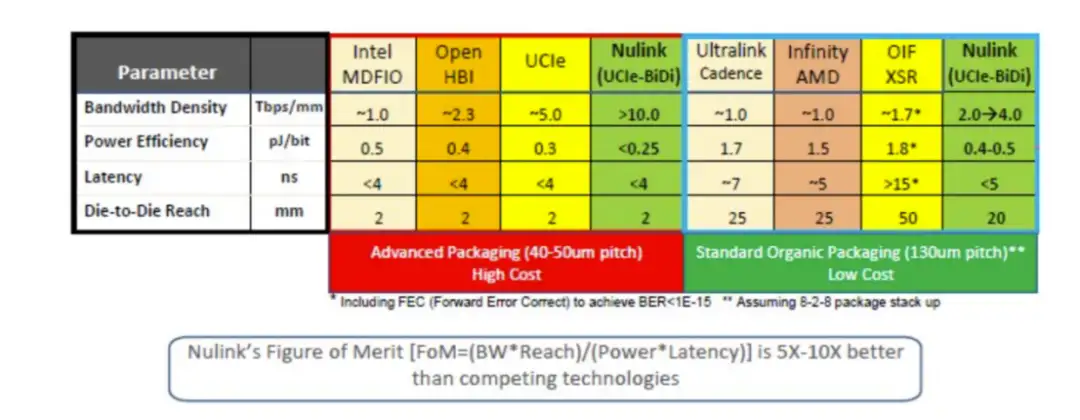

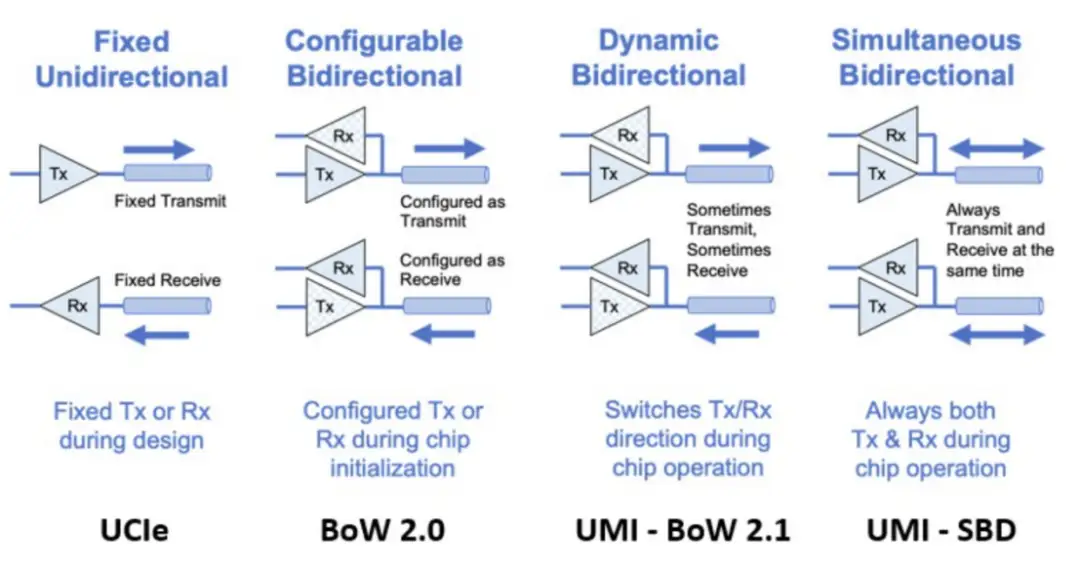

当 NuLink 于 2022 年 11 月首次推出时,它还没有这个名字,Eliyan 还没有提出使用 PHY 创建通用内存接口(UMI)的方法。NuLink 只是一种实现 UCI-Express 小芯片互连协议的方法,并支持 Farjadrad 和他的团队在几年前创建的原始 Bunch of Wires(BoW)小芯片互连所支持的任何协议,并作为拟议标准捐赠给开放计算项目。以下是 Eliyan 如何将 NuLink 与各种内存和小芯片互连协议进行堆叠:

Intel MDFIO 是 Multi-Die Fabric I/O 的缩写,用于将「Sapphire Rapids」至强 SP 处理器中的四个计算小芯片相互连接;EMIB 用于将这些小芯片链接到具有 HBM 的 Sapphire Rapids 的 Max 系列 CPU 变体的 HBM 内存堆栈。OpenHBI 基于 JEDEC HBM3 电气互连,也是 OCP 标准。我们在这里写的 UCI-Express 是一种时髦的 PCI-Express,带有 CXL 相干性覆盖层,旨在成为小芯片的晶粒到晶粒互连。英伟达(Nvidia)的 NVLink 现在用于将 Blackwell GPU 复合体上的小芯片粘合在一起,但该表中缺少英特尔的 XeLink,用于「Ponte Vecchio」Max 系列 GPU 上的 GPU 小芯片。与 UCI-Express 不同,NuLink PHY 是双向的,这意味着您可以拥有与 UCI-Express 一样多或更多的电线,但走线的带宽增加了一倍或更多。

如您所见,有一种昂贵的封装选项,它使用凸块间距为 40 微米到 50 微米的凸块,而裸片到芯片的距离仅为 2 毫米左右。PHY 的带宽密度可能非常高(小芯片上每毫米海滩的带宽密度为 Tb/秒),并且功率效率因方法而异。延迟也全面低于 4 纳秒。

在表格的右边是互连 PHY,它们可以与标准的有机基板封装一起使用,并使用 130 微米的凸块,因此是更便宜的选择。其中包括 Cadence 的 Ultralink PHY、AMD 的 Infinity Fabric PHY、Alphawave Semi 的 OIF 超短距离(XSR)PHY 以及 NuLink 版本。

更长的链路打开了计算和内存复合体的几何形状,并且还消除了 ASIC 和 HBM 之间的热串扰效应。堆叠内存对热量非常敏感,随着 GPU 越来越热,需要冷却 HBM 才能正常工作。如果你能让 HBM 离 ASIC 更远,你就可以更快地运行 ASIC(Farjadrad 估计大约 20%),而且温度更高,因为内存不够近,无法直接受到 ASIC 热量增加的影响。

此外,通过移除 GPU 等设备中的硅中介层或等效物,并转向有机基板并使用更胖的凸块和间隔组件,您可以将具有十几个 HBM 堆栈的双 ASIC 设备的制造成本从大约 12,000 美元(芯片加封装良率约为 50%)降低到良率为 87% 的设备(成本约为 6,800 美元)。

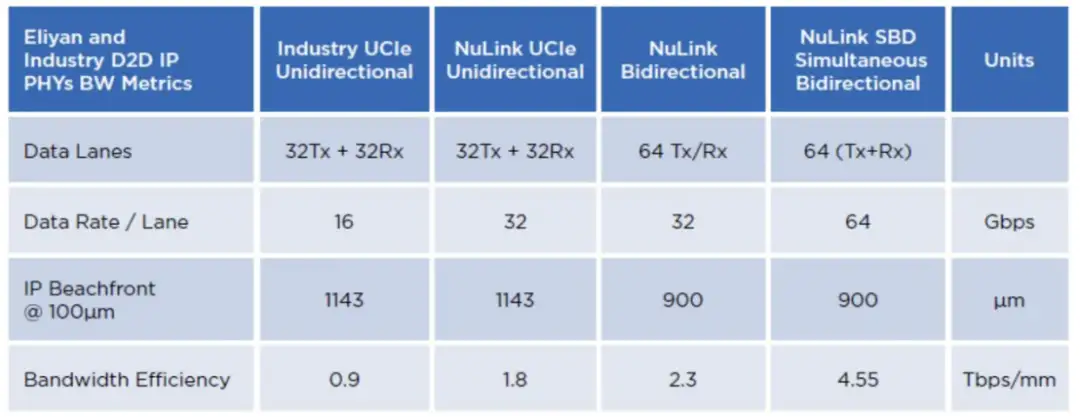

再看两个对比 UCI-Express、BoW 和 UMI 的图表。

正如你所看到的,Eliyan 一直在推动其 PHY 的双向功能,现在有能力同时进行双向流量,它称之为 UMI-SMD。

因此,NuLink PHY(现在被命名为 UMI)比 UCI-Express 更小、更快,你能用它做什么?

首先,您可以构建更大的计算引擎:

24 个或更多的 HBM 堆栈和 10 到 12 个重构的计算引擎包如何吸引您?这种设备需要四分之一到五分之一的时间来制造,因为它是在标准的有机基材上。在 1990 年代初,IBM 从 1989 年左右的巅峰开始下滑后,曾经有一句话与 IBM 挂钩:你可以找到更好的,但你不能支付更多。

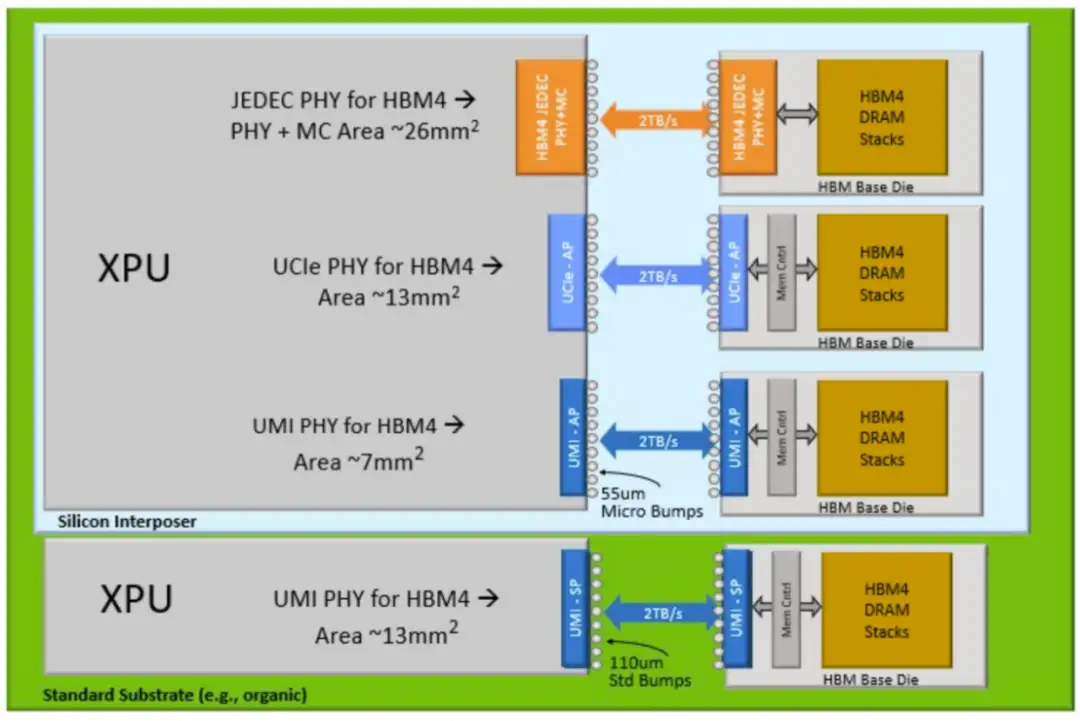

以下是 Eliyan 认为 HBM4 在未来可能会发挥的作用:

使用 NuLink UMI PHY 几乎可以再次将其切成两半,为您选择的 XPU 留出更多的逻辑空间。或者,如果你想放弃中介层,制造一个更大的设备,并忍受一个 13 平方毫米 UMI PHY,你也可以构建一个更便宜的设备,并且仍然从每个 HBM4 堆栈中驱动 2 TB/秒。

早在 2022 年 11 月,当 Eliyan 提出其想法时,它就将带有连接到其 HBM 内存的中介层的 GPU 与移除中介层并将 ASIC 加倍的机器进行了比较(就像 Blackwell 所做的那样),并将 24 个 HBM 排名与这些 ASIC 小芯片进行了对比。

左边是 Nvidia A100 和 H100 GPU 及其 HBM 内存的架构。中间是一张 Nvidia 图表,显示了随着 AI 应用程序可用的更多 HBM 内存容量和更多 HBM 内存带宽,性能如何提高。众所周知,H200 配备 141 GB HBM3E 内存和 4.8 TB/秒带宽,其工作量是 H100 的 1.6 到 1.9 倍,具有完全相同的 GH100 GPU,但只有 80 GB 的 HBM3 内存,3.35 TB/秒带宽。

内存不是功耗的很大一部分,GPU 才是,我们迄今为止看到的少量证据表明,Nvidia、AMD 和 Intel 投入该领域的 GPU 都受到 HBM 内存容量和带宽的限制——并且已经存在了很长时间,因为制造这种堆叠内存的困难。这些公司生产的是 GPU,而不是内存,他们通过提供尽可能少的 HBM 内存来对抗强大的计算量,从而最大限度地提高收入和利润。它们总是比上一代显示更多,但 GPU 计算总是比内存容量和带宽增长得更快。Eliyan 提出的设计可以使计算和内存恢复平衡,并使这些设备更便宜。

也许这对 GPU 制造商来说有点太强大了,所以随着 UMI 的推出,该公司已经退缩了一点,并展示了如何使用中介层和有机基板以及 NuLink PHY 的混合来制造更大、更平衡的 Blackwell GPU 复合体。

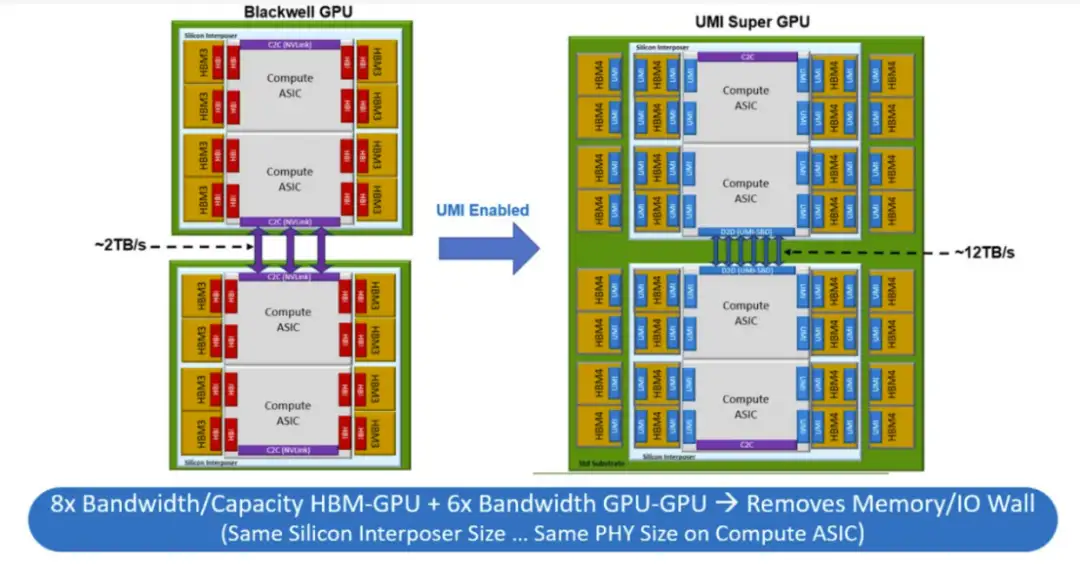

左下方是如何创建一个 Blackwell-Blackwell 超级芯片,该芯片具有一个以 1.8 TB/秒的速度运行的单个 NVLink 端口,将两个双小芯片 Blackwell GPU 连接在一起:

使用 NuLink UMI 方法,如上图右侧所示,有两个端口在两个 Blackwell GPU 之间提供大约 12 TB /秒的带宽 - 略高于 Nvidia 提供的 10 TB /秒 NVLink 端口,这些端口在 B100 和 B200 中将两个 Blackwell 芯片压缩在一起。这是 Eliyan 超级芯片设计的带宽的 6 倍,而不是 Nvidia B200 超级芯片设计(如果有的话)。如果 Nvidia 想要坚持其 CoWoS 制造工艺,Eliyan 可以在中介层上放置相同的 8 组 HBM3E 内存,但它可以在每个 Blackwell 设备上再放置 8 组 HBM3E,总共 32 组 HBM3E,这将产生 768 GB 的容量和 25 TB/秒的带宽。

这种 UMI 方法适用于任何 XPU,也适用于任何类型的存储器,你可以做这样疯狂的事情,所有这些都在一个巨大的有机基板上,不需要中介层:

任何存储器、任何共同封装的光学器件、任何 PCI-Express 或其他控制器都可以使用 NuLink 链接到任何 XPU。至此,插槽真的变成了主板。

对于更大的综合体,Eliyan 可以构建 NuLink Switch。

评论