基于CH365的PIC通信卡的设计

pci是先进的高性能局部总线,可同时支持多组外围设备。pci局部总线不受制于处理器,为中央处理器及高速外围设备提供数据传输通道,进行总线之间数据传输的调度管理,pci采用高度综合化的局部总线结构,以确保计算机中各部件、附加卡及系统之间的可靠运行。基于现在市场上pci芯片有plx公司及amcc公司的器件,他们在硬件设计周期以及驱动程序开发上对于初学者来讲都存在一定困难。ch365是一个连接pci总线的通用接口芯片,支持i/o端口映射、存储器映射、扩展rom以及中断。ch365将32位高速pci总线转换为简便易用的类似于isa总线的8位主动并行接口,用于制作低成本的基 于pci总线的计算机板卡、以及将原先基于isa总线的板卡升级到pci总线上。另外ch365不论在设计难度、开发周期、isa移植,还是在价格上都有其自身优越性,所以ch365应用非常广泛,例如适用于高速实时的i/o控制卡、通讯接口卡、数据采集卡、电子盘、扩展rom卡等。

1 ch365的特点

(1)可以设定pci板卡的设备标识(vendor id,device id,class code等)。

(2)支持以字节、字或双字为单位对i/o端口或者存储器进行读写。

(3)自动分配i/o基址,支持长达240b的i/o端口。

(4)支持本地硬件定址功能,自由选择i/o地址,在指定地址实现i/o端口。

(5)直接升级isa的i/o板卡到pci总线,完全不需要修改原isa卡的相关软件。

(6)直接映射支持容量为32kb的存储器sram或者扩展rom(boot rom)。

(7)无需外接元器件扩容支持容量为64kb以及128kb的存储器或者扩展rom。

(8)支持扩展rom无硬盘引导,支持闪存flash memory在线升级。

(9)可以提供扩展rom应用的子程序库brm,用于bios环境下用户界面显示及数据处理。

(10)支持低电平有效的本地中断请求,支持中断共享。

(11)提供两线串行主机接口,可以挂接类似24c0x的两线串口e2prom器件。

(12)内置4μs-1ms的硬件计时单元,用于软件运行过程中作为延时参考。

(13)芯片本身无需驱动程序即可工作,升级isa板卡可以不需要驱动程序。

2 空间映射

pc机中包括3种空间:存储器空间、i/o空间、配置空间。存储器空间主要包括内存、显存、扩展rom、设备缓冲区等,一般用于存放大量数据和进行数据块交换。i/o空间主要包括设备的控制寄存器和状态寄存器,一般用于控制和查询设备的工作状态以及少量数据的交换。配置空间主要用于向系统提供设备自身的基本信息,并接受系统对设备全局状态的控制和查询。为了避免地址冲突,pci总线要求各个设备所占用的地址能够重定位。重定位是由设备的配置空间的基址寄存器实现的,通常情况下,各个设备的基址寄存器总是被bios或者操作系统分配为不同的基址,从而将各个设备分别映射到不同的地址范围。在需要时,应用程序也可以自行修改基址。ch365的存储器空间占用32kb,偏移地址是0000h-7fffh,可以全部提供给外部设备使用,实际地址是存储器基址加上偏移地址。ch365的i/o空间占用256kb,去掉ch365自用寄存器,还可以提供240b给外部设备使用,偏移地址是00h-efh,实际地址是i/o基址加上偏移地址。

3 本地端信号线引脚

本地端信号线引脚如表1所示。

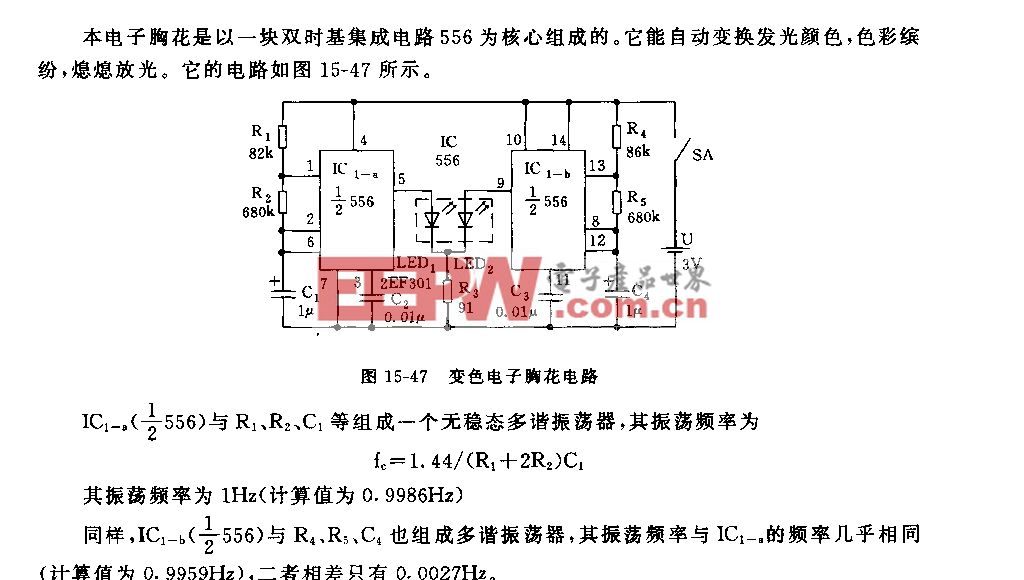

4 基于ch365的pci通信卡原理框图

基于ch365的pci通信卡由pci接口部分、ch365接口芯片、译码电路、本地总线4部分构成,如图1所示。

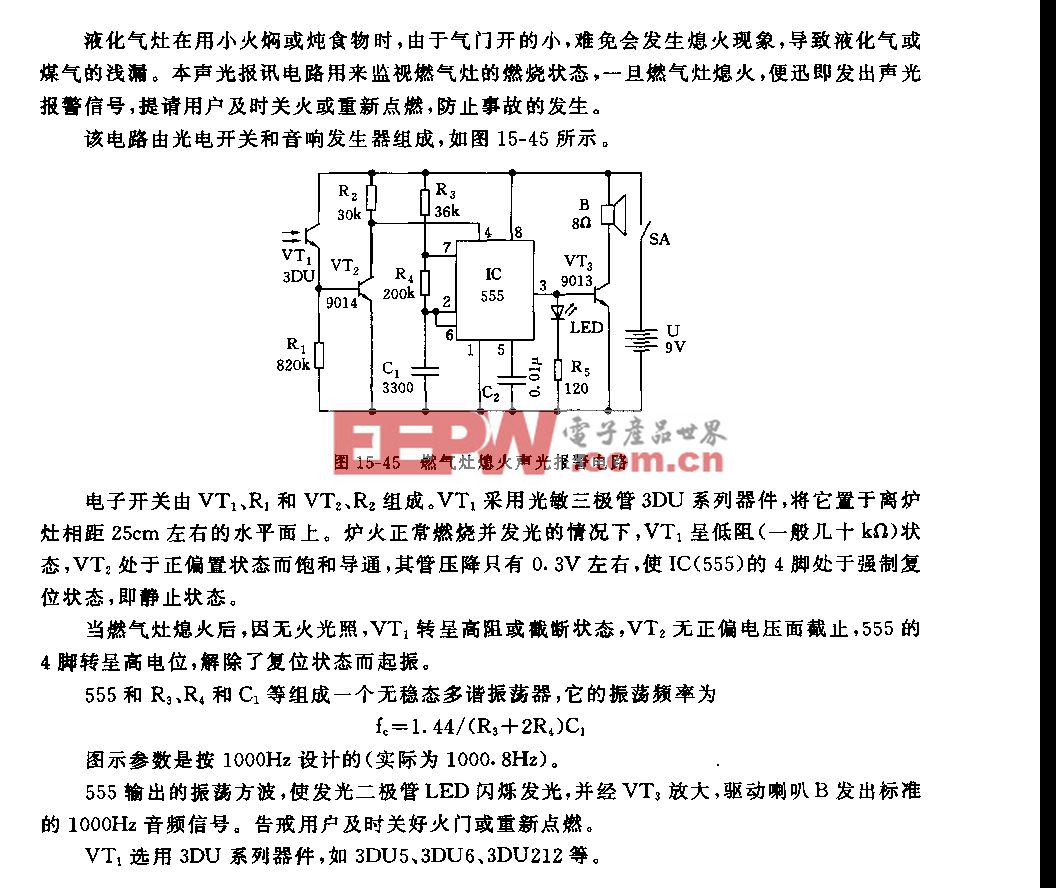

4.1 译码电路产生

在设计中采用传统74ls138产生本地8位总线地址,使用ch365地址a0,a1,a2以及读写控制信号参加译码。74ls138将地址译码输出2路读控制和2路写控制,经过74ls245或74ls574来控制输入和输出,如图2所示。

4.2 pci卡制作及pcb图设计注意事项

pci总线工作在高频环境中,传送线在信号线上驱动电压变化时会出现阻抗,信号线的宽度和到接地的距离都会影响其阻抗,所以在设计pcb时需要参考pci总线规范,特别要注意考虑信号阻抗匹配,具体有以下几点作为参考:

(1)在32位pci总线中,除了信号线外,还有2个卡存在信号:prsnt1#和prsnt2#。pci板卡设计者在卡存在信号上对卡的最大电源需求进行编码,当卡被插在pci插槽中时,他将其中至少一个或所有两个卡存在信号接地。

(2)对于32位pci总线的所有信号,其最大电路长度限定在1.5in(约38mm)以内。建议在设计pcb时,pci信号线的长度都小于25mm,尽量走弧线或者45°线,避免走直角或者锐角走线,并且尽量将走线布在元件面,而pcb背面保留大面积的接地覆铜,以降低传送线的阻抗。

(3)pci总线的clk信号线的长度要求是2.5in(约83mm)左右,并且只能与卡上一个负载连接。建议clk信号线的长度尽量保持在50-85mm之间,并且不宜靠近其他信号线,为减少周边信号线的干扰,在clk两侧及pcb背面布置接地线或者覆铜。

(4)ch365有3对电源引脚,至少需要3个电源退耦电容。

(5)与pci插槽连接的电源线引脚可以自由选择,但数量不宜少于4对。当板卡的电源消耗较大时,可以多增加几对电源线,通过多点接触提供稳定的大电流。

4.3 硬件中断功能介绍

ch365芯片具有软件和硬件中断功能,与中断功能有关的2个引脚分别是pci_inta和sys_ex。如果ch365的数据线d3连接了下拉电阻,则工作模式设定为启用中断功能,sys_ex引脚自动复用为int_req,作为本地中断请求输入引脚,低电平有效,外部电路需要请求计算机中断时只要向该引脚提供低电平脉冲。pci_inta总是作为pci中断三态输出引脚,不用中断功能时可以悬空不接,需要中断功能时可以与pci总线的inta相连接,低电平有效,中断激活时输出低电平,中断未激活时输出高阻。

5 应用程序介绍

(1)接收数据子程序

ch365opendevice(true,true);

mpch365_io_reg miobase;

ch365getiobaseaddr(&miobase);

//ch365writeiobyte(&miobase->mch365ioport

[0x0fa],71);//* * * * * * * * * *

uchar data1;

ch365readiobyte(&miobase->mch365ioport[m_portnumr],&data1);m_datar=data1;

(2)发送数据子程序

ch365opendevice(true,true);

mpch365_io_reg miobase;

ch365getiobaseaddr(&miobase);

ch365writeiobyte(&miobase->mch365ioport[m_portnumw],m_dataw);

本文采用南京沁恒公司提供的pci接口芯片ch365实现了pci通信卡的设计,在使用中测的实际传输率为10mb/s左右,工作稳定可靠,完全可以满足一般数据量传输不是非常快的场合。

评论