如何使用STATECAD进行多状态机设计实例分析

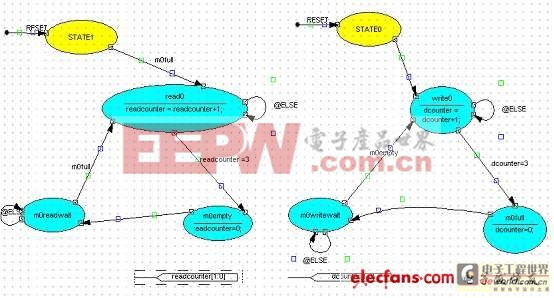

负责对M0读的状态机包括四个状态:

STATE1:读状态机复位后初始化

Read0:对M0读,读4个转到M0empty

M0empty:M0空状态

M0readwait:等待。M0空时转入Read0状态

负责对M0写的状态机必须知道M0是空的,而负责对M0读的状态机必须知道M0是满的才能读。读完了通知负责对M0写的状态机M0是空的,可以写了。二个状态机同时并行工作。M0写的状态机在写操作完了,就等待M0空。M0读的状态机在读操作完了,就等待M0满。在STATECAD中,状态本身可以作为其他状态机的转移条件。这也正是在进行多状态机的协同设计中最需要的功能,能大大方便多状态机的设计。

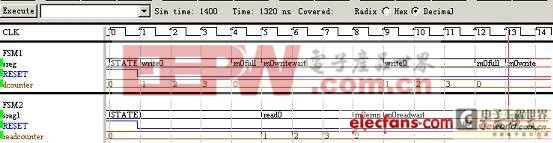

输入完状态图,就基本完成了状态机的设计过程。进行逻辑优化(工具自动进行逻辑优化)后,使用STATEBENCH进行状态转移分析。以下是自动状态转移模拟波形。

由以上的波形看到状态机的工作过程符合设计逻辑。对单独的器件操作也许不需要采用多状态机的设计方法,但在多器件需要并行工作时,多状态机的协同设计就显得必要了。导出VHDL模型块到ISE中进行仿真后综合,这里就不多讲了,以下是产生的代码:

-- D:XILINXTUTORIALDUOZTJI.Vhd

LIBRARY Ieee;

USE Ieee.Std_logic_1164.All;

LIBRARY Ieee;

USE Ieee.Std_logic_unsigned.All;

ENTITY SHELL_DUOZTJI IS

评论