基于SOC的SPI接口设计与验证

摘要:给出了一个可用于SoC设计的SPI接口IP核的RTL设计与功能仿真。采用AMBA 2.0总线标准来实现SPI接口在外部设备和内部系统之间进行通信,在数据传输部分,摒弃传统的需要一个专门的移位传输寄存器实现串/并转换的设计方法,采用复用寄存器的方法,把移位传输寄存器和发送寄存器结合在一起,提高了传输速度,也节约了硬件资源。采用SoC验证平台进行SoC环境下对IP的验证,在100 MHz时钟频率下的仿真和验证结果表明,SPI接口实现了数据传输,且满足时序设计要求。

本文引用地址://m.amcfsurvey.com/article/234922.htm0 引言

SPI(Serial Peripheral Interface)是一种同步串行总线接口,很多器件如E2PROM、FLASH、实时时钟、A/D转换器等都用到了SPI接口,它也是SoC中的一个常用外围功能模块。AMBA总线是由ARM公司开发的一种高性能、开放性SoC系统总线,它主要包括AHB,ASB和APB三种总线类型。AHB总线主要用于连接高性能、高速度的系统模块,如CPU,DSP,SRAM等;APB总线主要用于连接低速外围模块,如UART,I2C等,接口简单,效率高,功耗低;ASB总线通过连接系统高速部件来实现高速通信,一般较少用到。

本文设计一个可作为IP核用于SoC设计的SPI接口,采用AMBA2.0总线标准来实现SPI接口在外部设备和内部系统之间进行通信,SPI接口作为低速外围模块挂载在APB总线上。

1 SPI接口的定义

1.1 接口信号

SPI的接口信号为同步串行时钟SCLK、主机输入/从机输出MISO、主机输出/从机输入MOSI、从机选择

(低电平有效),由于只用到四根线工作,与其他接口相比具有结构简单、速度快的优点。SPI有主/从两种工作模式,SPI总线的串行时钟SCLK用来同步数据传输,在主模式下由主机产生,从机选择信号

用来决定外部设备是否被选作SPI的从设备。主从设备连接方式如图1所示。

1.2 内部寄存器

SPI的内部寄存器如表1所示。

1.3 传输时序

在本设计中,SPI的传输时序由控制寄存器CTRL来决定。CTRL[9]定义为RX_NEGE,置1表示数据在时钟下降沿接收,置0为上升沿接收;CTRL[10]定义为TX_NEGE,置1表示数据在下降沿发送,置0为上升沿发送;CTRL[11]定义为LSB,置1表示数据从最低位开始传输,置0从最高位开始传输。CTRL[6:0]定义为CHAR_LEN,为数据传输长度,最长可为128 b。以其中一种传输时序为例说明,如图2所示。

2 SPI接口的RTL设计

本设计是针对SoC系统的,目标是实现适用于SoC设计并且符合SPI通信协议的IP核,实现SoC通过此SPI接口和外设通信。所以,本设计分成SPI主机模块spi_master的设计和SPI从机模块spi_slave的设计,采用Verilog HDL进行RTL设计。

2.1 spi_master模块设计

spi_master的功能主要包括:

(1)实现主机通过APB总线初始化spi_master的寄存器;

(2)实现spi_master和spi_slave之间的数据交换。

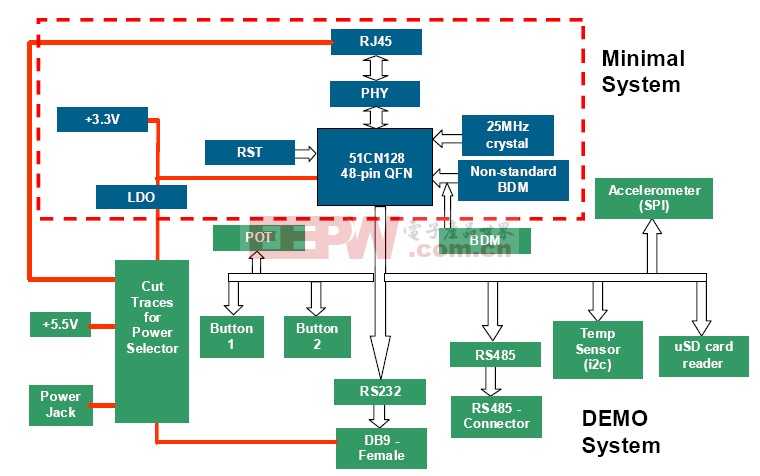

因此,spi_master模块主要就是实现分频和串并转换,主要包含时钟产生子模块spi_clgen和数据传输子模块spi_shift,其设计结构如图3所示。

2.1.1 时钟产生子模块设计

该子模块主要作用是产生SPI主/从设备通信所需的同步串行时钟sclk。在主模式下,sclk由系统提供的时钟信号pclk分频产生,产生的串行时钟的时钟频率由式(1)计算得来:

传输开始前,cnt载人DIVIDER值,满足传输条件下cnt减1计数,减为0时,输出时钟clk_out翻转,并且在clk_out的上升沿和下降沿分别产生pos_edge和neg_edge信号。

2.1.2 数据传输子模块设计

该子模块的主要功能是完成数据的串/并转换。在本设计中,该子模块负责把内部APB总线并行传输进来的数据转化成串行数据传输给SPI从设备,并且把外部SPI从设备串行传输进来的数据转化成并行数据传入到APB总线上。

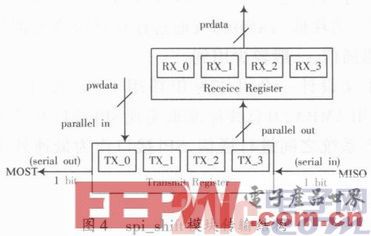

传统的串/并转换设计方法需要一个专门的移位传输寄存器,本设计采用了复用寄存器的方法,把移位传输寄存器和发送寄存器结合在一起。当传输停止且总线锁存使能时,数据从APB总线并行传输到spi_shift移位传输寄存器即发送寄存器TxX,然后在传输时钟使能情况下串行输出到MOSI;而在主机接收使能的情况下,由从机MISO串行输人数据至spi_shift移位传输寄存器。传输结构如图4所示,从图4可以看出,数据传输位宽最大可达128 b/s。

2.1.3 RTL代码设计

spi_master模块代码设计划分如下:

(1)寄存器选择使能信号的地址译码电路;

(2)读寄存器部分,将并行数据输出到APB总线上;

(3)控制寄存器ctrl、时钟分频寄存器divider、从机选择寄存器ss初始化部分;

(4)例化时钟分频子模块和数据传输子模块。

为了提高代码的复用性,特别设计了一个宏定义模块,主要定义了传输最大位数SPI_MAX_CHAR,分频寄存器位数SPI_DIVIDER_LEN,从机选择数目SPI_SS_NB等相关数据。

2.2 spi_slave模块设计

评论