处理器核改进 引发能耗地震

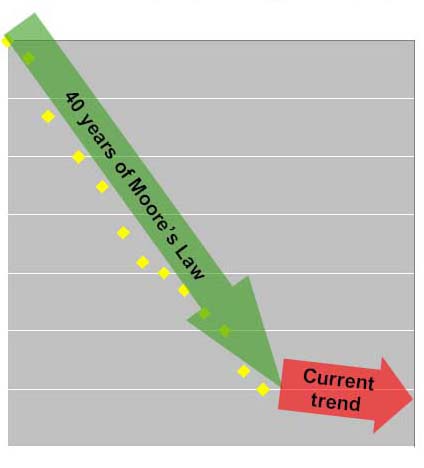

根据摩尔定律,每18个月(起初是24个月)芯片上的晶体管密度就会翻番,但是前几年功耗问题曾一度困扰Intel等公司的发展。为此,Intel对摩尔定律进行了大胆的修正,指出摩尔定律是晶体管密度、性能和功耗的折中发展规律。为此,多核开创了一个崭新的计算时代。

本文引用地址://m.amcfsurvey.com/article/82667.htm

图1 原摩尔定律不再有助于功耗降低

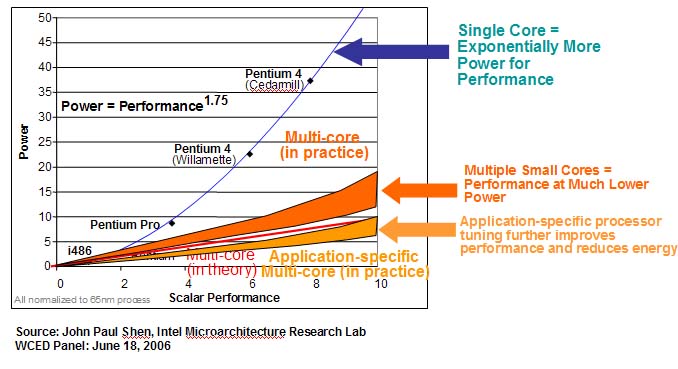

通常认为,多核设计与优化的处理器相互协同作用,才能带来芯片能耗降低的地震(图2)。多年来一直倡导在SoC中进行多核设计,在可配置多核方面独树一帜的Tensilica,在多核低功耗方面取得了巨大的突破,产品已经应用于Cisco ASR 1000F系列产品上,Cisco的QuantumFlow处理器采用了40核方案,Epson公司的PM-D870打印机采用了6核设计。

图2 特殊应用处理器对改进性能和降低功耗帮助最大

在近日旧金山举行了Electronic Summit2008上,Tensilica公司的总裁兼CEO Chris Rowen博士称该公司处理器核功耗是其竞争对手的1/3,并介绍了开发秘籍:

1, 优化指令。Tensilica每个优化指令效率相当于普通的5~50个RISC指令;

2, 处理器核数量增加,但每个核几何尺寸更小,每个小核完成专门的功能,例如有的做无线通信、有的管协议,有的处理视频,有的音频……;在整体设计时,如果需要控制功能,控制核可以是Tensilca的,也可以是ARM或MIPS等公司的。

3, 处理器核接口方面,为了方便实现多核,需要新的通讯支持,Tensilca的Xtensa处理器核有更多的指定内存(memory-mapped)I/O和直接连接选择。

4, 建模和模拟工具Xenergy Energy Explorer在结构上进行了突破,包括建模和分析,软件开发和调试等。

晶体管相关文章:晶体管工作原理

晶体管相关文章:晶体管原理

评论