基于LEON3处理器和Speed协处理器的复杂SoC设计实现*

3)由160个实数浮点乘法累加运算器组成40个复数乘法累加器阵列,1Mbit的双口SRAM,8个512×32bit系数ROM,两个直角到极坐标转换电路,两个对数变换电路及其它辅助电路和控制电路。

本文引用地址://m.amcfsurvey.com/article/94563.htm

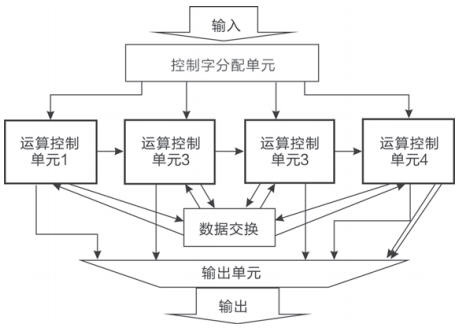

图1 Speed的内部模块结构

Speed传统的工作方式是通过片外FPGA输入控制信号和待处理数据,这不仅增大了PCB板级布线、调试的工作量,而且FPGA不能用C等高级语言编程,算法改动起来不灵活。另一方面,随着半导体工艺、微电子技术的发展,大规模的复杂SoC实现技术逐渐成熟,因此有必要将板级FPGA + Speed改进为芯片级MCU + Speed,这样既能实现真正的可编程增大灵活性,又能加快用户开发信号处理系统的速度。

评论