基于LEON3处理器和Speed协处理器的复杂SoC设计实现*

图9 触发中断响应的zero_flag信号

本文引用地址://m.amcfsurvey.com/article/94563.htm

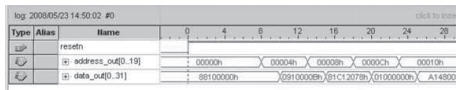

图10 在Altera StratixII 2S180中的仿真结果

结语

本项目利用LEON3的高性能、易编程、开源等优点,开发了AHB总线接口和DMA控制器,实现了Speed专用信号处理器的软件可编程,大大简化了Speed用户的开发过程。有待改进之处是,1)当前Speed可处理40bit数据,而Leon3是32bit,没有最大限度发挥Speed的运算能力;2)如果在LEON3上运行RTEMS (Real Time Executive for Multiprocessor Systems) 操作系统,将进一步方便用户扩展LEON3的利用价值。

参考文献:

[1]Gaisler Research, www.gaisler.com

[2]王振荣, 王伟勋. 基于CPCI总线的通用信号处理平台研究[J],现代电子技术,2007.7

[3]郭二辉, 洪一, 汪颢等. GA3816器件在时域脉冲压缩处理中的应用[J], China Science and Technology Information, 2006.6

评论