Cadence针对28纳米工艺为TSMC模拟/混合信号设计参考流程1.0版提供广泛支持

全球电子设计创新领导厂商Cadence设计系统公司今天宣布,支持台湾积体电路制造股份有限公司 (以下简称TSMC) 模拟/混合信号(以下简称AMS)设计参考流程1.0版,以实现先进的28纳米工艺技术。Cadence与TSMC在这项全新设计参考流程上的合作,将可协助促进高级混合信号设计的上市时间,帮助降低在设计基础架构的多余投资,并提高投资回报率。

本文引用地址://m.amcfsurvey.com/article/110542.htm“与Cadence之间的合作伙伴关系,是客户实现高级模拟/混合信号设计成功不可或缺的一环,”TSMC设计方法与服务行销副处长Tom Quan说。“针对28纳米工艺的TSMC 模拟/混合设计参考设计流程,藉由运用最新工艺技术的优势,推出目前业界最完整的设计、检验与生产芯片的方法学。我们非常乐于与Cadence公司以及整个TSMC开放创新平台 (Open Innovation Platform™) 生态系统继续合作,以确保我们的技术能够跟上新兴设计挑战的脚步,让我们的客户在设计基础架构方面的投资发挥最大价值。”

这个设计参考流程强化为设计团队提供强大的辅助,帮助他们完成高效、低成本芯片实现的任务,可称为Cadence EDA360战略的主要支柱。

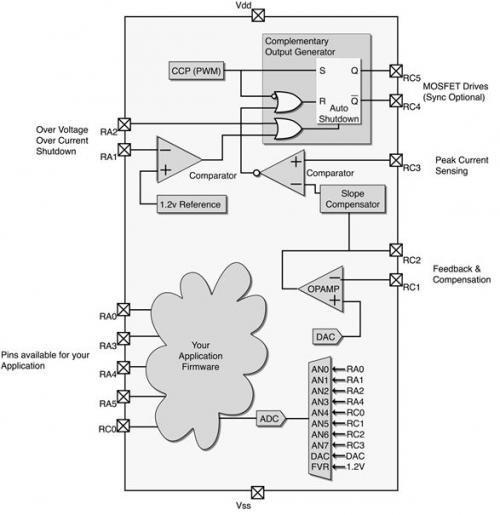

Cadence公司混合信号技术为TSMC崭新的28纳米设计参考流程提供非常全面的产品支持,一步步协助设计迈向芯片实现。Cadence公司与TSMC的合作解决当今在无线、网络、消费电子与其它应用方面, 芯片设计中模拟与混合信号功能方面越来越高的复杂性与集成度。

“随著无线、网络、消费电子与CPU设计复杂度的日益增加,模拟与混合信号IP可以占到芯片设计的50%以上,”产品管理部门主管Sandeep Mehndiratta说。“Cadence支持的TSMC模拟/混合信号设计参考流程1.0版,专为TSMC芯片技术而优化化,为客户提供全面的设计、验证与设计实现解决方案,帮助他们在28纳米工艺节点上实现高级混合信号设计的最高质量。”

TSMC设计参考流程融合来自Virtuoso平台的各种Cadence技术阵容,涵盖在28纳米工艺的AMS IP设计、验证与设计实现。在先进28纳米设计经验证的技术基础上,Cadence 与TSMC合作,原理图设计、AMS验证、射频与瞬态噪声分析、良品率灵敏度分析、约束导向型布局、模拟布置与布线、物理验证、DFM感知的寄生提取、IR压降与电迁移分析。

评论