- 传统 I2S—为何要包括系统时钟?

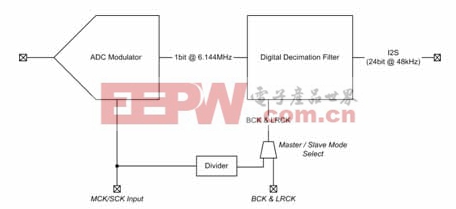

过去,我们在讨论音频话题时,偶尔会提及 I2S。我在以前的一些文章中提到过 I2S,其他人在做音频研究时也都会提到它。简而言之,它是一种将立体声数据从一端传输至另一端的同步

- 关键字:是从老板时钟音频

- 关键词:I2S、主时钟、MCK、PLL、BCK、LRCK、压控振荡器、VCO、音频、模拟、半导体、德州仪器、TI信号链基础知识#54 谁是音频时钟的“老板”,谁是主,谁又是从呢?作者:Dafydd Roche,德州仪器 (TI) 音

- 关键字:信号链基础时钟音频

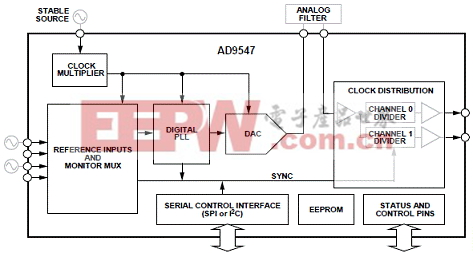

- AD9547是双路/四路输入网络时钟发生器/同步器,能为许多系统包括同步光网络(SONET/SDH)提供同步.输入基准频率从1 kHz 到750 MHz,频率监视1ppm,输出频率高达450MHz,主要应用在网络同步,OC-192的SONET/SDH时钟,无线基站

- 关键字:方案同步时钟网络AD9547

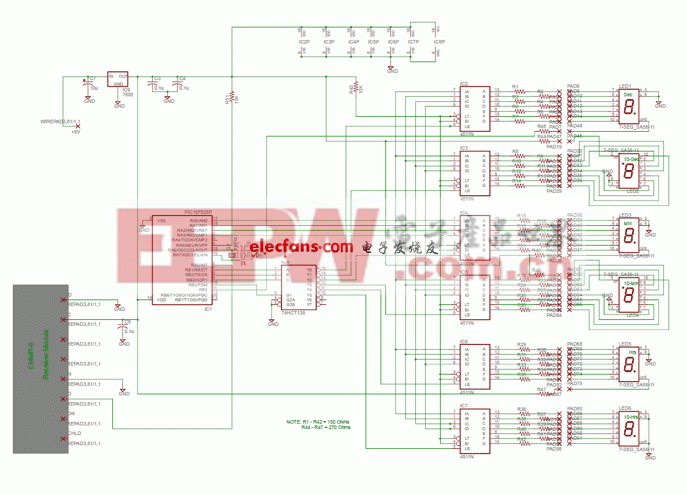

- 我们以一个实际的时钟电路来说明定时器的软件编程方法,时钟就是我们最为常见的显示时、分、秒为单位的计时工具,它是典型的应用代表。

时钟的最小计时单位是秒,但使用单片机定时器来进行计时,若使用6.0MHz

- 关键字:介绍原理电路时钟

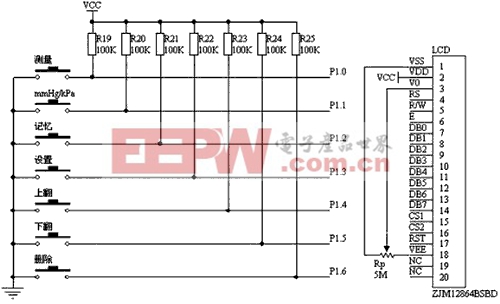

- 键盘和显示电路

如下图所示,由键盘电路和液晶显示电路两部分组成。液晶显示电路采用ZJM12864BSBD,这是一款低功耗的点阵图形式LCD,显示格式为128点(列)times;64点(行),具有多功能指令,很容易与MPU相连。其

- 关键字:电路存储时钟日历键盘显示

- 随着今天模数转换器的数据转换采样速度进入到每秒千兆次采样(GSPS),系统需要能够支持这样高的转换速度,模拟器件必须产生和放大高频信号。除了模拟信号路径外,设计师需要完全了解采样时钟和高比特率数据获取电路方

- 关键字:高速数据转换系统时钟数据传输

- 时钟树优化与有用时钟延迟在 “后端时序修正基本思路” 提到了时序优化的基本步骤。其中,最关键的阶段就是时钟树建立。基本的优化都优先在数据路径上进行,并且希望路径尽量的短,最好在一个时钟周期之内

- 关键字:时钟树时钟

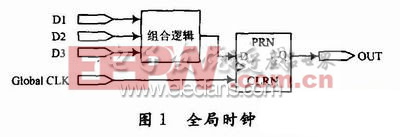

- 基于FPGA的时钟设计,对于一个设计项目来说,全局时钟是最简单和最可预测的时钟。在PLD/FPGA设计中最好的时钟方案是由专用的全局时钟输入引脚驱动的单个主时钟去钟控设计项目中的每一个触发器。只要可能就应尽量在设计项目中采用全局时钟

- 关键字:设计时钟FPGA基于

- 摘要:本应用笔记介绍如何对Maxim的DS314xx时钟同步IC进行现场升级,使其接受并锁定至1Hz输入时钟信号。文章探讨了少数情况下对1Hz时钟监测功能及系统软件支持的需求。基于这些考虑,系统利用DS314xx器件构建标准的

- 关键字:时钟1Hz输入工作IC同步DS314xx升级

- 摘要:文中从控制信号和数据通路两个方面入手,设计了信号在不同时钟域之间的同步电路。采用直接锁存法和锁存反馈法来控制信号的跨时钟域传递,电路简洁、高效;采用异步FIFO (First In First Out)实现数据信号的同步

- 关键字:电路设计同步时钟信号不同数字

- PIC WWVB时钟设计,有很多DIY WWVB在网络上的时钟设计的版本。商业的“原子”的钟表价格便宜和广泛使用,但我想试试我的手,在设计一个获得接收到WWVB的洞察和了解一点点编程PIC单片机。我的版本是不是最简单的,但它工作得很

- 关键字:设计时钟WWVBPIC

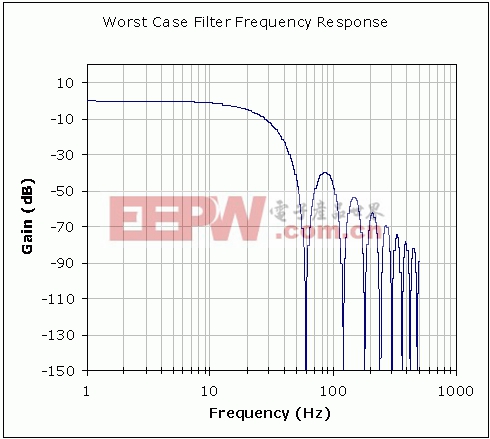

- 摘要:本文探讨了时钟公差对Sigma;-Delta; ADC中低通抽样和数字滤波器的影响,特别是对滤波器陷波频率的影响。窄带Sigma;-Delta;应用通常利用数字滤波器提供50Hz、60Hz或50Hz/60Hz的噪声抑制。在选择外部时钟晶体

- 关键字:50Hz/60Hz噪声公差时钟高性能ADC理解

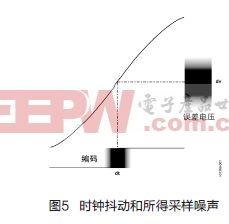

- 孔径抖动指孔径延迟中的样本间变化,在ADC输入中表现为频率相关噪声。对于高频模拟输入信号,抖动是采样过程中宽带噪声的主要来源。如图5所示,采样时钟上的噪声在所得采样信号上造成更多采样噪声。

- 关键字:时钟噪声201106

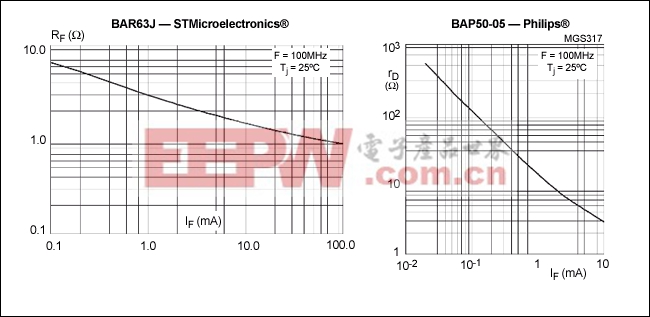

- 摘要:RF衰减是无线设计中的常见电路,本应用笔记详细描述了几种采用PIN二极管和电流源DAC控制RF衰减的方法。

PIN二极管通常作为TV调谐器中的RF信号以及固定通信设备中宽带RF的可变衰减器。这类二极管可以作为分立

- 关键字:噪声抑制影响50Hz/60Hz公差高性能ADC时钟理解

时钟介绍

时钟的概念多用于数字语音交换机,因为数字交换对于以时隙为单位的交换单位而言,其时间性的重要程度非常高。为保证交换机的正常工作,每套交换系统都必须配置精度极高的时钟发生器,用于交换系统内部工作。系统内部的时钟一般称为内时钟。 如果两套交换系统协调工作,那么必须要在两套系统之家,也就是两个内时钟之间进行协调,保证两个时钟同步工作,这就是时钟同步,对于每套系统的内时钟而言,另一套系统的内时钟即为外时钟 [

查看详细]

关于我们-

广告服务-

企业会员服务-

网站地图-

联系我们-

征稿-

友情链接-

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473