- 1 RTC结构特点实时时钟的基本功能是保持跟踪时间和日期等信息,但许多RTC还提供有多种附加功能,如:看门狗定时器、系统复位、非易失存储器(NV RAM)、序列号、方波输出、涓流充电等。因此,在进行电路设计时,选择

- 关键字:电路设计时钟实时组图

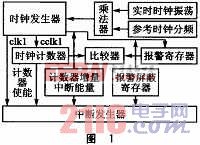

- 本文结合MSP430系列微处理器,详细论述了通过控制改变MCU的时钟频率来降低功耗的设计方法。 1 功耗产生的原因 在CMOS电路中,功耗损失主要包括静态功耗损失和动态功耗损失两部分。其中静态功耗主要是由反偏PN结

- 关键字:分析时钟动态MCU功耗

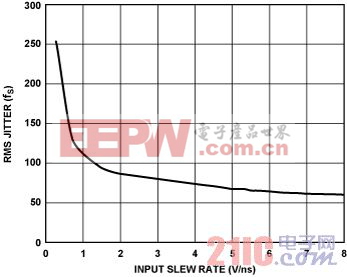

- 高速转换器时钟分配器件的端接,使用时钟分配器件1或者扇出缓冲器为ADC和DAC提供时钟时,需要考虑印刷电路板上的走线和输出端接,这是信号衰减的两个主要来源。时钟走线与信号摆幅

PCB上的走线类似于低通滤波器,当时钟信号沿着走线传输时,会造成

- 关键字:器件分配时钟转换器高速

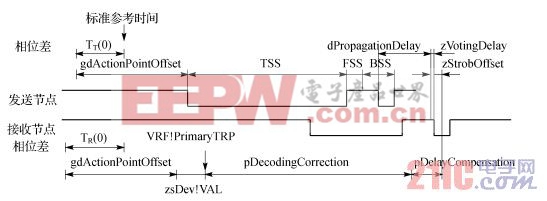

- 随着安全性要求的提高, CAN总线的带宽就嫌不足,消息送达的确定性不够。为此,一些汽车大厂和汽车电子的大厂成立了研发新型通信协议的联盟[1],目标是开发出称为FlexRay的协议,使它成为下一代车用通信协议的事实上

- 关键字:同向漂移同步时钟解决FlexRay如何

- 摘要:构建了一种基于ZigBee技术的公共时钟系统,依据ZigBee的不同技术,分别构建了它的总体结构、时钟同步算法以及软硬件结构。该公共时钟系统在某电站办公综合楼内经过一年的实验运行,结果表明系统时钟同步精度高

- 关键字:系统构建时钟公共ZigBee技术基于

- 摘要:实时时钟在工业系统中具有良好的应用前景。本系统以微控制器LPC2131为核心控制器,控制内部实时时钟,实现对秒、分、小时等各个时间寄存器的准确操作,通过串口将采集到的数据发送到上位机。本文详细给出硬件设

- 关键字:控制设计时钟实时LPC2131基于

- 摘要:研究了一种基于以太网物理层时钟同步的高带宽低噪声压控振荡器(VCO),该VCO采用交叉耦合的电流饥饿型环形振荡器,通过级联11级环路电路和改善其控制电压变换电路,优化了VCO的输出频率范围以及降低了输出时钟的

- 关键字:PLLVCO设计同步时钟以太网物理用于

- 回顾以太网同步技术的发展,我们曾在以太网上用过互联网网络时间协议NTP(Network Time Protocol)技术,简单网络时间协议SNTP(Simple Network Time Protocol)技术,GPS技术或用T1/E1和以太网组成混合网络来增加以太网

- 关键字:电信特性IP确保时钟同步精确

- 摘要:介绍了时钟日历芯片DS12C887的主要功能、特点和内部地址分布,给出了C8051F020与DS12C887的硬件接口电路和相关程序设计方法。

关键词:日历;时钟DS12C887;外部存储器;时钟

0 引言

DS12C887是Dalla

- 关键字:应用设计DS12C887芯片时钟日历新型

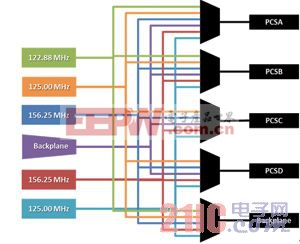

- 可编程时钟器件集成了主要的时序元件,如一个PLL、分频器、扇出缓冲器、零延迟缓冲器,从而节省电路板面积、降低成本,并提高性能。使用诸如ispClock5400D系列器件,设计人员可以更好地规划其特定系统的理想时钟产生和分配电路,更好地利用其FPGA上的I/O。

- 关键字:分配控制时钟FPGAI/O改进免费

- 针对目前测控系统中对时间控制的需要,结合实时时钟PS1288的类型与特点,提出一种基于单片机的日历时钟的设计方法。该系统以AT89C52单片机为控制核心,采用实时日历时钟芯片DS12887作为实时日历时钟芯片,为系统提供详细的年、月、日、星期和小时、分等时间信息。通过对DS12887的详细分析,设计其与单片机的硬件接口。阐述该系统的硬件构成和软件设计过程,并给出了相应的硬件原理图和软件流程图。结果表明,DS12887时钟芯片具有低功耗、外围接口简单、精度高、工作稳定可靠等优点,可广泛用于各种需要较高精度的

- 关键字:模块设计时钟日历单片机基于

- 在现代电子技术的设计与开发过程中. 特别是在通信、雷达、航空、航天以及仪器仪表等领域, 都需要进一步提高一系列高精度、高稳定度的频率源的频率精度, 频率合成器是无线通信设备中的一个重要组成部分, 其设计

- 关键字:4157ADF数字预失真时钟

- 摘要:为了产生语音调度系统中数据接收端异步接收PCM30/32路一次群串行数提流所需同步时钟的目的,采用以分频计数器为基础模块,辅以相位校正和误校正处理模块从已知速率PCM数据流中提取同步时钟信号的方法,利用可

- 关键字:PCM串行数据流时钟

- 摘 要:研究了门控时钟技术在130 nm工艺、基于高阈值标准单元库下的低功耗物理实现方法。详细阐述了多级门控时钟技术的作用机制和参数的设置方法,给出了基于门控时钟的后端实现流程,着重分析了插入门控时钟对时钟

- 关键字:实现方案电路功耗时钟基于

- 本文根据雷达发射机频率快速变化的特点,采用目前新型的逻辑控制器件研究新型频率测量模块,结合等精度内插测频原理,对整形放大后的脉冲直接计数,实现对下变频后单脉冲包络的载波快速测频。具有测量精度高,测量用

- 关键字:移相时钟测频模块设计

时钟介绍

时钟的概念多用于数字语音交换机,因为数字交换对于以时隙为单位的交换单位而言,其时间性的重要程度非常高。为保证交换机的正常工作,每套交换系统都必须配置精度极高的时钟发生器,用于交换系统内部工作。系统内部的时钟一般称为内时钟。 如果两套交换系统协调工作,那么必须要在两套系统之家,也就是两个内时钟之间进行协调,保证两个时钟同步工作,这就是时钟同步,对于每套系统的内时钟而言,另一套系统的内时钟即为外时钟 [

查看详细]

关于我们-

广告服务-

企业会员服务-

网站地图-

联系我们-

征稿-

友情链接-

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473