- 高性能模拟与混合信号IC领导厂商Silicon Labs(芯科实验室有限公司)今日宣布针对高速网络、通信和数据中心等当今互联网基础设施的根基,推出业界最高频率灵活性和领先抖动性能的时钟解决方案。Silicon Labs的新一代Si534x“片上时钟树“系列产品包括高性能时钟发生器和高集成度Multi-PLL抖动衰减器。这些单芯片、超低抖动时钟芯片整合了时钟合成与抖动衰减功能,设计旨在减少光传输网络、无线基础设施、宽带接入/汇聚、电信级以太网、测试和测量以及企业和数据中心设备(包

- 关键字:Silicon LabsMulti-PLL时钟

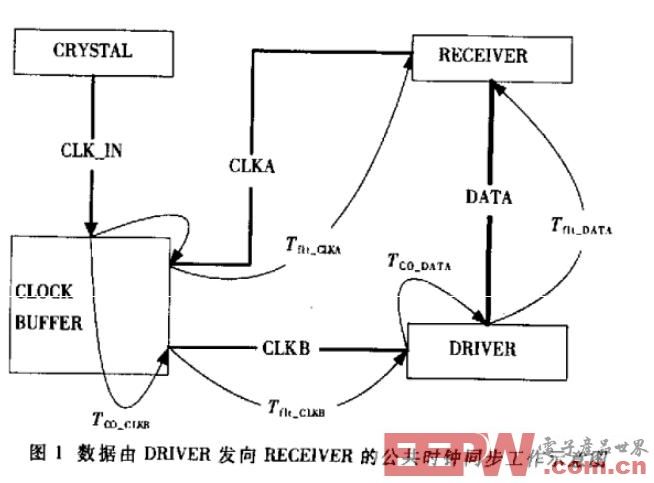

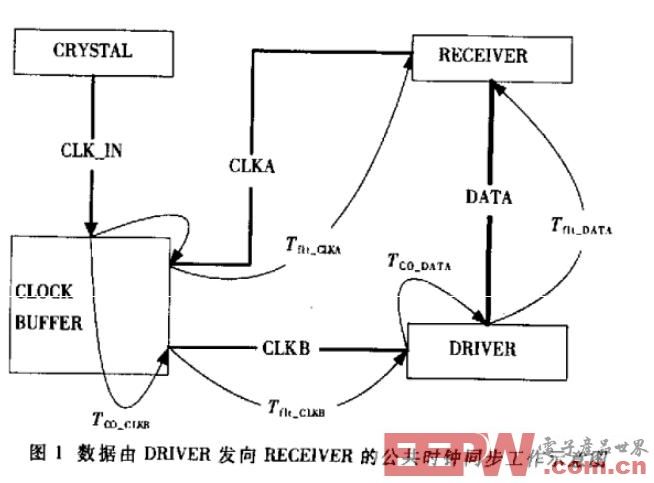

- 在网络通讯领域,ATM交换机、核心路由器、千兆以太网以及各种网关设备中,系统数据速率、时钟速率不断提高,相应处理器的工作频率也越来越高;数据、语音、图像的传输速度已经远远高于500Mbps,数百兆乃至数吉的背板也越来越普遍。数字系统速度的提高意味着信号的升降时间尽可能短,由数字信号频率和边沿速率提高而产生的一系列高速设计问题也变得越来越突出。当信号的互连延迟大于边沿信号翻转时间的20%时,板上的信号导线就会呈现出传输线效应,这样的设计就成为高速设计。高速问题的出现给硬件设计带来了更大的挑战,有许多从逻

- 关键字:PCB时钟时序

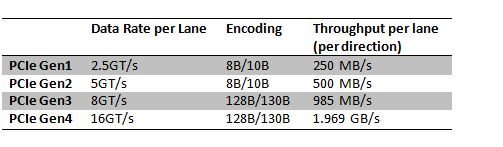

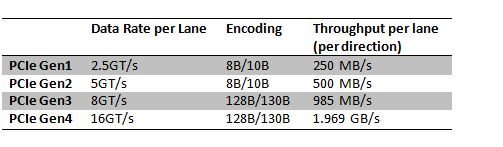

- PCI Express® (PCIe®) 是一项业界领先的标准输入/输出 (I/O) 技术,是服务器、个人电脑以及其它应用中最常用的 I/O 接口之一。该标准多年来不断发展,以适应更高的数据速率(见表 1)。第 3 代 PCIe 引入了全新的编码方案,其可在不增加数据速率一倍的情况下,将数据吞吐量提升一倍。PCI-SIG 近期宣布推出的第 4 代 PCIe 具有 16 G 每秒传输 (GT/s) 的比特率。第 4 代的规范预计将在 2014 或 2015 年发布。 表 1:各代

- 关键字:PCI Express时钟RefClk

- 时钟节拍是特定的周期性中断。这个中断可以看作是系统心脏的脉动。中断之间的时间间隔取决于不同的应用,一般在10mS到200mS之间。时钟的节拍式中断使得内核可以将任务延时若干个整数时钟节拍,以及当任务等待事件发生时,提供等待超时的依据。时钟节拍率越快,系统的额外开销就越大。 1、系统中断与时钟节拍 1.1、 系统中断 中断是一种硬件机制,用于通知CPU有个异步事件发生了。中断一旦被系统识别,CPU则保存部分(或全部)现场(context),即部分(或全部)寄存器的值,跳转到专门的子程序

- 关键字:UC/OS-II时钟中断机制

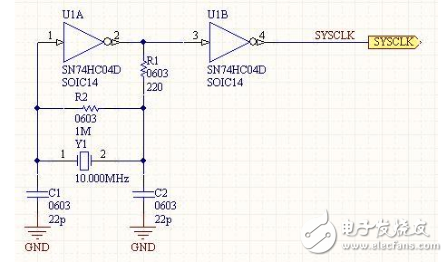

- 数字逻辑已经成为当今所有电子电路的核心,无论是FPGA、微控制器、微处理器还是分立逻辑。数字系统采用必须互连在一起以执行所需功能的众多组件。确保此类数字系统正常运行的要素是实现所有数字组件之间通信以及在其之间建立同步的时钟信号。因此,我们始终需要一种源头来生成这种时钟信号。 信号源采用振荡器的形式。虽然当今大多数微控制器具有集成RC振荡器,但是这种内部RC振荡器生成的时钟质量往往不足以支持与系统中其它模块通信所需要的精度。因此,需要采用能够为整个系统提供时钟信号并且满足对精度、信号完整性与稳定性

- 关键字:数字逻辑振荡器时钟

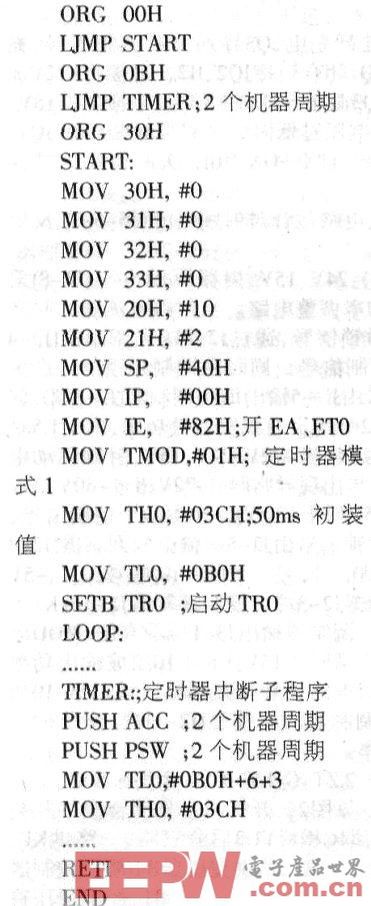

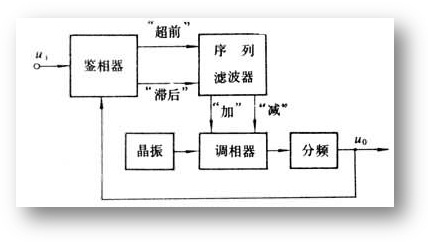

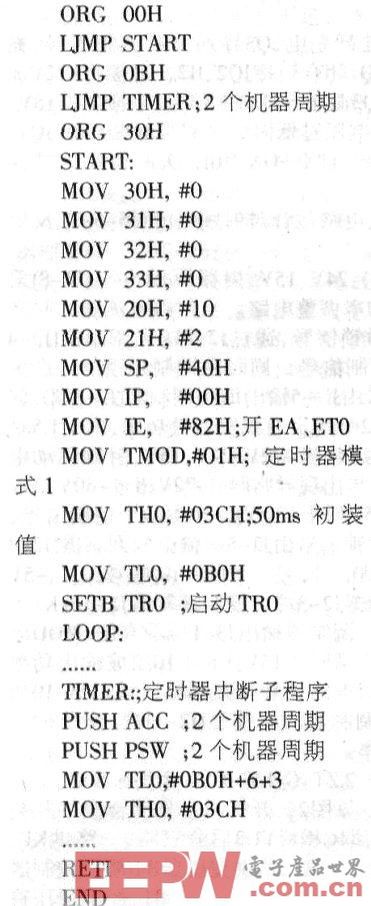

- 单片机应用中,常常会遇到这种情况,在用单片机制作电子钟或要求根据时钟启控的控制系统时,会突然发现当初校准了的电子时钟的时间竟然变快或是变慢了。 于是,尝试用各种方法来调整它的走时精度,但是最终的效果还是不尽人意,只好每过一段时间手动调整一次。那么,是否可使时钟走时更精确些呢?现探讨如下: 一、误差原因分析 1.单片机电子时钟的计时脉冲基准,是由外部晶振的频率经过12分频后提供的,采用内部的定时,计数器来实现计时功能。所以,外接晶振频率的精确度直接影响电子钟计时的准确性。 2.单片机电子时钟利用内部

- 关键字:单片机时钟

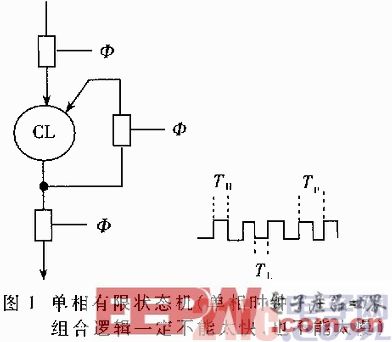

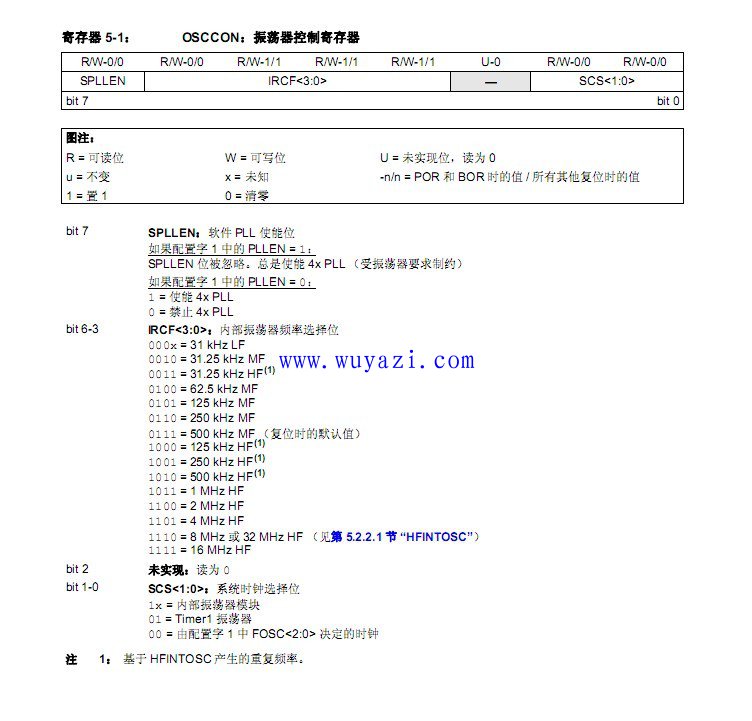

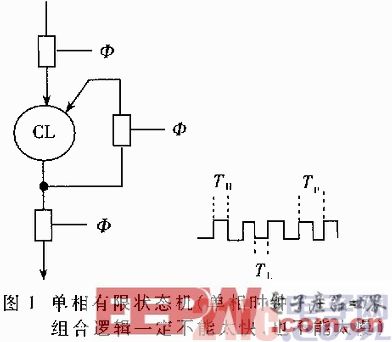

- 摘要:介绍了一个基于MCU内核的时钟系统的设计,给出了其电路结构并详细地分析了系统的工作原理。该系统能生成两相不重叠时钟,利用静态锁存器保存动态信息,提供三种电源管理方式以适应低功耗应用。在上华(CSMC)0.6μm工艺库下,利用Cadence EDA工具对电路进行了仿真,仿真结果验证了设计的准确性。 关键词:微控制器 时钟系统 两相不重叠时钟 时钟系统是微控制器(MCU)的一个重要部分,它产生的时钟信号要贯穿整个芯片。时钟系统设计得好坏关系到芯片能否正常工作。

- 关键字:MCU时钟

- 逻辑分析仪是利用时钟从测试设备上采集和显示数字信号的仪器,最主要作用在于时序判定。由于逻辑分析仪不...

- 关键字:逻辑分析仪时钟数字信号

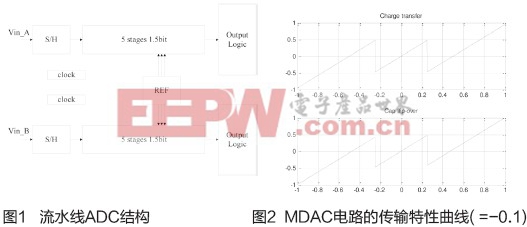

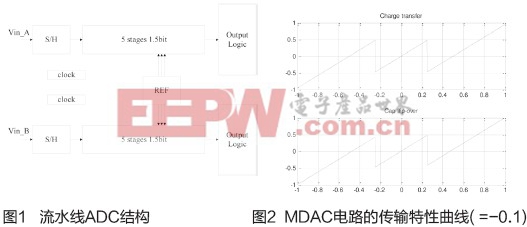

- 摘要:本文介绍了一款低功耗8位200MSPS的模数转换器。ADC是由时间交织和逐级递减技术来实现低功耗的。流水级和放大器的设计保证了低电流下满足工艺、电压、温度(PVT)变化。本ADC采用0.35μm 双层多晶硅栅三层金属的CMOS工艺,在200MHz采样频率和41MHz输入信号频率下达到47.7dB的SNDR。

- 关键字:ADC放大器无线通信流水线时钟201312

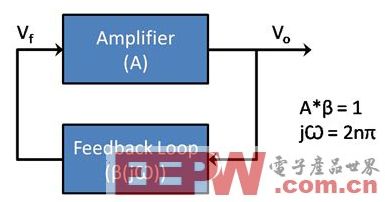

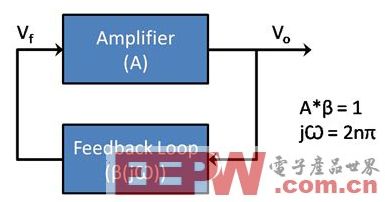

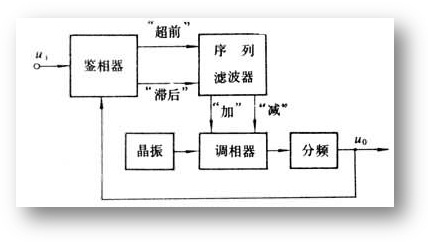

- STM32F系列微处理器,或者说是Cortex-M3内核的MCU内,都集成了一个叫PLL的东西。PLL就是锁相回路或锁相环(Phase Locked Loop),用来统一整合时脉讯号,使内存能正确的存取资料。PLL用于振荡器中的反馈技术,将外部的输入信号与内部的振荡信号同步,锁相环路的基本方框图如下图所示。一句话,PLL用来控制STM32F的时钟频率的。总而言之,STM32F系列MCU使用了这个东西,而我们在MCU上电之后,也就要对其正确的初始化,这样,我们才能得到我们需要的时钟配置。

- 关键字:微处理器STM32FPLLMCU时钟

- LED调光能以两种方式进行:模拟调光和脉冲宽度调制(PWM)调光。模拟调光简单地调节LED串的DC电流,以改变...

- 关键字:信号发生器时钟微型控制器

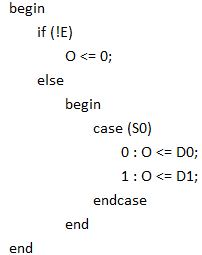

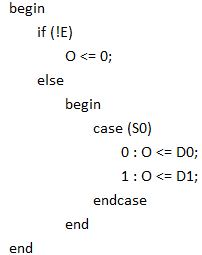

- 从大学时代第一次接触FPGA至今已有10多年的时间。至今记得当初第一次在EDA实验平台上完成数字秒表,抢答器,密码锁等实验时,那个兴奋劲。当时由于没有接触到HDL硬件描述语言,设计都是在MAX+plus II原理图环境下用74系列逻辑器件搭建起来的。

- 关键字:FPGAEDAVHDLVerilog时钟IP核

- 把握DCM、PLL、PMCD和MMCM知识是稳健可靠的时钟设计策略的基础。赛灵思在其FPGA中提供了丰富的时钟资源,大多数设计人员在他们的FPGA设计中或多或少都会用到。不过对FPGA设计新手来说,什么时候用DCM、PLL、PMCD和MM

- 关键字:FPGATips时钟资源

- 数字系统的设计师们面临着许多新的挑战,例如使用采用了串行器/解串器(SERDES)技术的高速串行接口来取代传统的...

- 关键字:高速串行接口时钟SERDES接口

- TD-SCDMA系统时钟指标TD-SCDMA基站的时间同步需求描述见技术规范3GPPTR25.836,要求提供NodeB的物理层...

- 关键字:恒温晶振TD-SCDMA时钟

时钟介绍

时钟的概念多用于数字语音交换机,因为数字交换对于以时隙为单位的交换单位而言,其时间性的重要程度非常高。为保证交换机的正常工作,每套交换系统都必须配置精度极高的时钟发生器,用于交换系统内部工作。系统内部的时钟一般称为内时钟。 如果两套交换系统协调工作,那么必须要在两套系统之家,也就是两个内时钟之间进行协调,保证两个时钟同步工作,这就是时钟同步,对于每套系统的内时钟而言,另一套系统的内时钟即为外时钟 [

查看详细]

关于我们-

广告服务-

企业会员服务-

网站地图-

联系我们-

征稿-

友情链接-

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473