DDR3 SDRAM内存的总线速率达到600 Mbps to 1.6 Gbps (300 to 800 MHz),1.5V的低功耗工作电压,采用90nm制程达到2Gbits的高密度。这个架构毫无疑问更快、更大,每比特的功耗也更低,但是如何实现FPGA和DDR3 SDRAM DIMM条的接口设计呢? 关键字:均衡(leveling) 如果FPGA&nbs

关键字:FPGA DDR3 SDRAM 接口 模拟IC 电源

在高速数字视频系统应用中,使用大容量存储器实现数据缓存是一个必不可少的环节。SDRAM就是经常用到的一种存储器。 但是,在主芯片与SDRAM之间产生的时序抖动问题阻碍了产品的大规模生产。在数字电视接收机的生产实际应用中,不同厂家的PCB板布线、PCB材料和时钟频率的不同,及SDRAM型号和器件一致性不同等原因,都会带来解码主芯片与SDRAM间访问时序的抖动问题。 本文利用C-NOVA公司数字电视MPEG-2解码芯片AVIA9700内置的SDRAM控制器所提供的时序补偿机制,设计了一个方便使

关键字:嵌入式系统 单片机 SDRAM 时序控制 MCU和嵌入式微处理器

引言 同步动态随机存储器(SDRAM),在同一个CPU时钟周期内即可完成数据的访问和刷新,其数据传输速度远远大于传统的数据存储器(DRAM),被广泛的应用于高速数据传输系统中。基于FPGA的SDRAM控制器,以其可靠性高、可移植性强、易于集成的特点,已逐渐取代了以往的专用控制器芯片而成为主流解决方案。然而,SDRAM复杂的控制逻辑和要求严格的时序,成为开发过程中困扰设计人员主要因素,进而降低了开发速度,而且大多数的基于FPGA的SDR

关键字:工业控制 嵌入式系统 单片机 FPGA SDRAM 嵌入式 工业控制

1 引言随着雷达技术发展,大带宽高分辨力、多种信号处理方式的采用,使得实时信号处理对数据的处理速度大大提高。同时在雷达信号处理中运算量大,数据吞吐量急剧上升,对数据处理的要求不断提高。随着大规模集成电路技术的发展,作为数字信号处理的核心数字信号处理器(DSP)得到了快速的发展和应用。ADSP-TS201DSP是美国模拟器件(ADD公司继TSl01之后推出的一款高性能处理器。此系列DSP性价比很高,兼有FPGA和ASIC信号处理性能和指令集处理器的高度可编程性,适用于大存储量、高性能、高速度的信号处理和图像

关键字:模拟技术 电源技术 SDRAM DSP-TS201 总线接口 模拟IC 电源

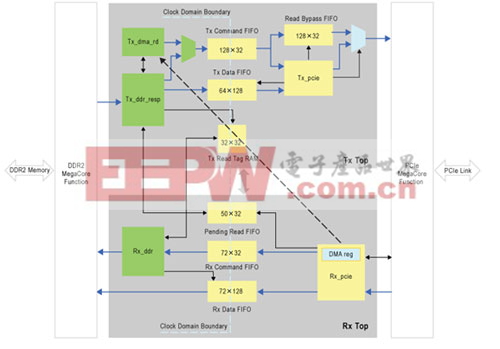

Altera PCI Express到DDR2 SDRAM 参考设计,OverviewAltera offers a PCI Express to DDR2 SDRAM reference design that demONSTrates the operation of Alteras PCI Express (PCIe) MegaCorereg; product. This reference design provides an interface betw

关键字:参考 设计 SDRAM DDR2 PCI Express Altera

Altera宣布,在FPGA业界实现了对高性能DDR3存储器接口的全面支持。在最近通过的JESD79-3 JEDEC DDR3 SDRAM标准下,Altera Stratix® III系列FPGA可以帮助设计人员充分发挥DDR3存储器的高性能和低功耗优势,这类存储器在通信、计算机和视频处理等多种应用中越来越关键。 这些应用处理大量的数据,需要对高性能存储器进行快速高效的访问。符合JESD79-3 JEDEC DDR3 SDRAM标准可满足DDR3存储器的1.5V低功耗电压供电要求,在下一

关键字:Altera SDRAM 存储器

MIPS科技宣布,Kawasaki Microelectronics(K-micro)已采用 MIPS-Based™ Topaz 先进 SoC 计算子系统,进军快速增长的无源光网络(PON)市场。采用 MIPS32®24Kc™ 和 24Kf™ 处理器的 Topaz 有助于 PON 设计师更快更有效地推出高性能设备。K-m

关键字:MIPS-Based SoC Topaz 计算子系统 消费电子 SoC ASIC 消费电子

在DSP应用系统中,需要大量外扩存储器的情况经常遇到。例如,在数码相机和摄像机中,为了将现场拍摄的诸多图片或图像暂存下来,需要将DSP处理后的数据转移到外存中以备后用。从目前的存储器市场看,SDRAM由于其性能价格比的优势,而被DSP开发者所青睐。DSP与SDRAM直接接口是不可能的。 FPGA(现场可编程门阵列)由于其具有使用灵活、执行速度快、开发工具丰富的特点而越来越多地出现在现场电路设计中。本文用FPGA作为接口芯片,提供控制信号和定时信号,来实现DSP到SDRAM的数据存取。 1 SDRA

关键字:DSP FPGA SDRAM 单片机 嵌入式系统 存储器

在数字图像处理、航空航天等高速信号处理应用场合,需要有高速大容量存储空间的强力支持,来满足系统对海量数据吞吐的要求。通过使用大容量同步动态RAM(SDRAM)来扩展嵌入式DSP系统存储空间的方法,选用ISSI公司的IS42S16400高速SDRAM芯片,详细论述在基于TMS320C6201(简称C6201)的数字信号处理系统中此设计方法的具体实现。 1 IS42S16400芯片简介IS42S16400是ISSl公司推出的一种单片存储容量高达64 Mb(即8 MB)的16位字宽高速SDRAM芯片。

关键字:DSP SDRAM 单片机 嵌入式系统 存储器

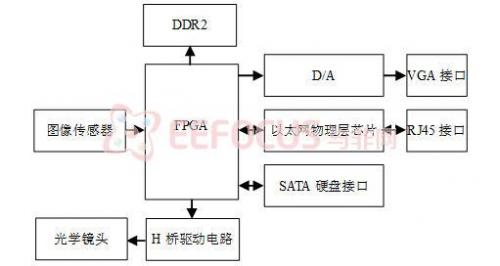

笔者在研究有关文献的基础上,根据具体情况提出一种独特的方法,实现了对SDRAM的控制,并通过利用FPGA控制数据存取的顺序来实现对数字视频图像的旋转,截取、平移等实时处理。

关键字:SDRAM 视频处理器

介绍Registered SDRAM的工作原理和接口芯片,以及在MPC8241嵌入式系统中进行Registered SDRAM电路设计的实例;给出电路原理设计和PCB布局布线的一般规则。

关键字:istered SDRAM 8241 Reg

介绍了SDRAM的特点和工作原理,提出了一种基于FPGA的SDRAM控制器的设计方法,使用该方法实现的控制器可非常方便地对SDRAM进行控制。

关键字:Verilog SDRAM FPGA 控制器

前言 机械视觉应用在各种产业的生产制造及品质检测已是行之有年, 利用机械视觉可以提升检测精度或加速生产速度,因此逐渐变成许多生产检测设备必备的一环。 目前市面上的影像检测系统大多采用面扫描(Area-scan)的摄影机进行影像的采集及分析, 但是随着产品尺寸的加大(例如:PCB, LCD面板, 晶圆), 在提高产能及精度的要求下, 面扫描摄影机的分辨率及取像速度无法满足这些要求的事实开始浮上枱面, 而系统业者也开始意识到线扫描(Line-scan)摄影机的分辨率及取像速度才能满足这些时势所驱的产业需

关键字:PS-based 测试测量

sdram-based介绍

您好,目前还没有人创建词条sdram-based!

欢迎您创建该词条,阐述对sdram-based的理解,并与今后在此搜索sdram-based的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473