- 恒忆 (Numonyx) 与三星电子 (Samsung Electronics Co., Ltd) 宣布将共同开发制定相变存储器 (Phase Change Memory,PCM) 产品的市场规格,此新一代存储技术可满足载有大量内容和数据平台的性能及功耗要求,从而帮助多功能手机及移动应用、嵌入式系统*、高级运算装置的制造商应对设计挑战。制定针对PCM 产品的通用软硬件兼容标准,将有效简化设计流程并缩短产品开发时间,使制造商能在短时间内采用这两家公司推出的高性能、低功耗 PCM 存储产品。 相较于

- 关键字:NumonyxNANDNORPCMSDRAM

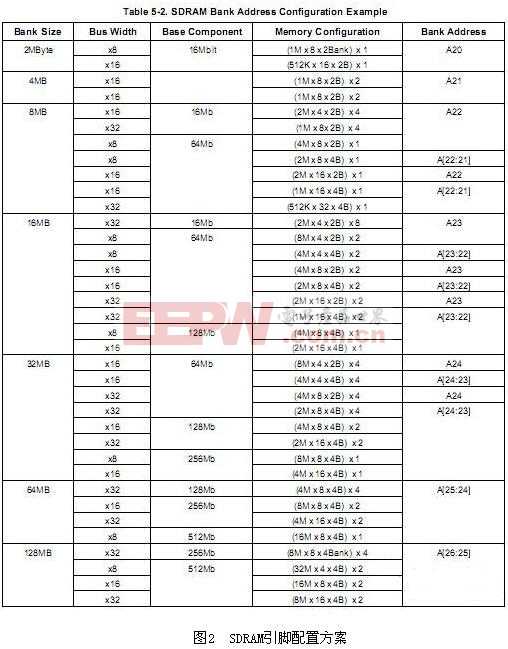

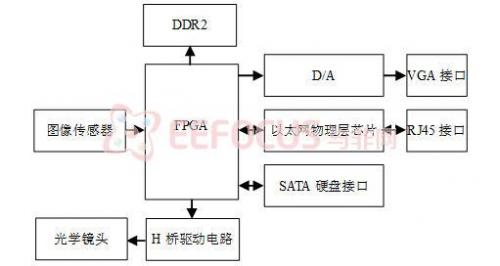

- 大容量SDRAM在windows CE系统中的应用设计,摘 要:扩大同步动态随机存储器(SDRAM)的容量是提升嵌入式产品性能的关键问题。这里基于Intel公司的PXA255处理器提出一种大容量sDRAM的硬件设计方法,并在微软提供的板级支撑包(BSF’)的基础上编写了一套在win―dows

- 关键字:应用设计系统CESDRAMwindows大容量

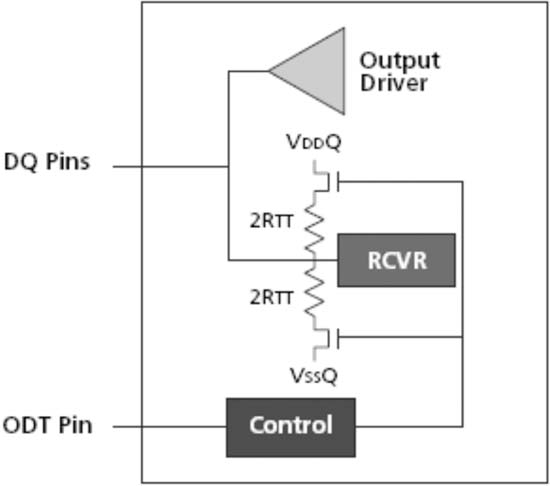

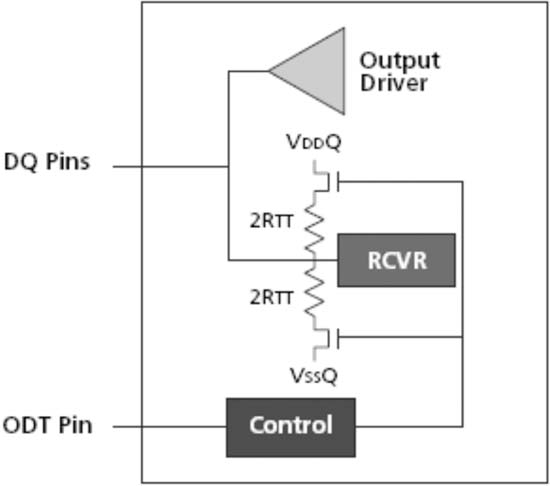

- DDR2(Double Data Rate 2,两倍数据速率,版本2) SDRAM,是由JEDEC标准组织开发的基于DDR SDRAM的升级存储技术。 相对于DDR SDRAM,虽然其仍然保持了一个时钟周期完成两次数据传输的特性,但DDR2 SDRAM在数据传输率、延时、功耗等方面都有了显著提高,而这些性能的提高,主要来源于以下技术的提升:ODT,Post CAS,4n数据预取,封装等。

- 关键字:思科DDR2 SDRAM

- 极高性能的浮点DSP,比以往的 SHARC处理器性能提高一倍,具有硬件加速器与音频应用提升特性: 片上存储器增加60%以上,提供DDR2 SDRAM外部存储器接口及连接端口 中国 北京——Analog Devices, Inc.(纽约证券交易所代码: ADI),全球领先的高性能信号处理解决方案供应商,最新推出SHARC® ADSP-21469,以帮助开发人员重新定义专业系统中的逼真音响。更多的通道、更多的效果、更多的建模、更高的采样速率:专业数字音频应用正在不断逼

- 关键字:DSPSHARC处理器DDR2 SDRAMADI

- 任意波形发生器在雷达、通信领域中发挥着重要作用,但目前任意波形发生器大多使用静态存储器。这使得在任意波形发生器工作频率不断提高的情况下,波形的存储深度很难做得很大,从而不能精确地表达复杂信号。本文介绍的基于动态存储器(SDRAM)的设计能有效解决这一问题,并详细讨论了一种简化SDRAM控制器的设计方法。

- 关键字:SDRAM任意波形发生器中的应用

- 摘 要:采用OV2610的CMOS图像传感器和26K色的TFT液晶屏,在SOPC上集成了OV2610、TFT液晶控制器和DMA控制器,实现了图像数据流的采集和显示。 关键词:DMA Avalon数据流模式 SDRAM 随着大规模集成电路设计技术的进步、制造工艺水平的提高以及单个芯片上的逻辑门数的增加,嵌入式系统设计变得日益复杂。把整个系统集成到一个芯片上,即片上系统SoC(System on Chip)技术是当前嵌入式系统设计的一个研究热点。在Altera公司提供的

- 关键字:SoCDMAAvalon数据流模式SDRAM

- 引言 DDR3 SDRAM存储器体系结构提高了带宽,总线速率达到了600 Mbps至1.6 Gbps (300至800 MHz),它采用1.5V工作,降低了功耗,90-nm工艺密度提高到2 Gbits。这一体系结构的确速率更快,容量更大,单位比特的功耗更低,但是怎样才能实现DDR3 SDRAM DIMM和FPGA的接口呢?调平技术是关键。如果FPGA I/O结构中没有直接内置调平功能,和DDR3 SDRAM DIMM的接口会非常复杂,成本也高,需要采用大量的外部元件。那么,什么是调平技术,这一技

- 关键字:FPGA存储器DDR3SDRAM

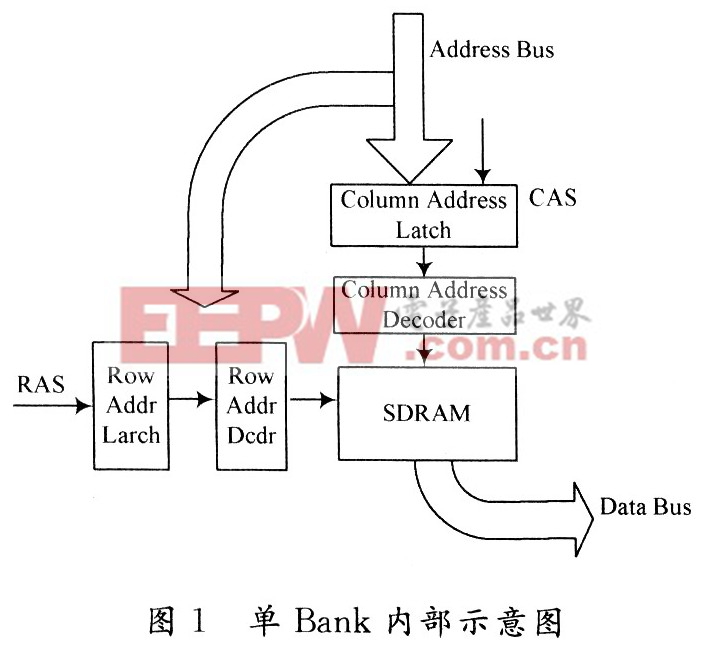

- RAM(随机存取存储器 是一种在电子系统中应用广泛的器件,通常用于数据和程序的缓存。随着半导体工业的发展,RAM获得了飞速的发展,从RAM、DRAM(Dynamic RAM,即动态RAM)发展到SDRAM(Synchronous Dynamic RAM,即同步动态RAM),RAM的容量越来越大、速度越来越高,可以说存储器的容量和速度已经成为半导体工业水平的标志。 1 任务背景 SDRAM具有大容量和高速的优点,目前其存取速度可以达到100~133MHz,单片容量可以达到64Mbit或更高

- 关键字:VHDLSDRAM存储器微处理器

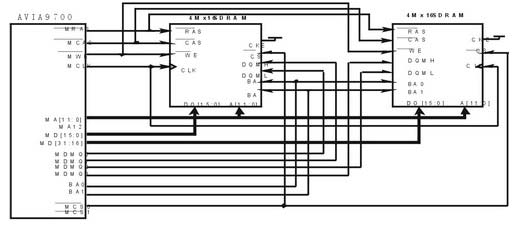

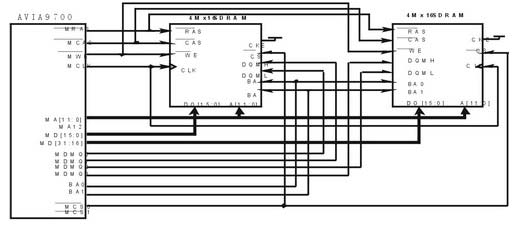

- 在高速数字视频系统应用中,使用大容量存储器实现数据缓存是一个必不可少的环节。SDRAM就是经常用到的一种存储器。 但是,在主芯片与SDRAM之间产生的时序抖动问题阻碍了产品的大规模生产。在数字电视接收机的生产实际应用中,不同厂家的PCB板布线、PCB材料和时钟频率的不同,及SDRAM型号和器件一致性不同等原因,都会带来解码主芯片与SDRAM间访问时序的抖动问题。 本文利用C-NOVA公司数字电视MPEG-2解码芯片AVIA9700内置的SDRAM控制器所提供的时序补偿机制,设计了一个方便使

- 关键字:SDRAM数字电视

- 随着笔记本电脑、手机等移动终端以及家用数码产品的大规模增长,器的移动性和能耗问题已广泛受到业界关注。日前,(全球半导体组织)委员会会议在上海举行,推动存储工业新标准制定。 在过去五年内,JEDEC曾与中国半导体行业组织合作,促进中国及世界的半导体行业标准。例如中国电子标准协会(CESA),中国半导体行业协会(CSIA)与中国电子标准研究所(CESI)等。 我国企业已占JEDEC会员数的20%,而且数目还在增长。JEDEC本次会议主要研究了DDR3 SDRAM(第三代双倍速率同步动态随机存储

- 关键字:SDRAMDRAM

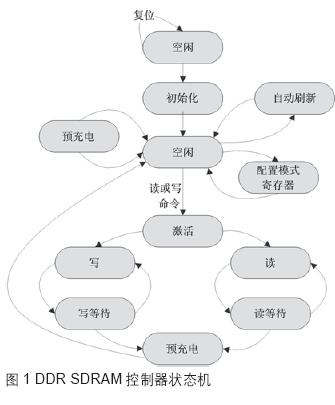

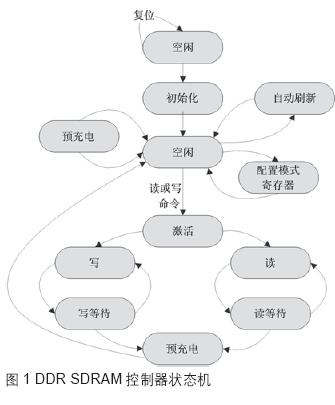

- 实现数据的高速大容量存储是数据采集系统中的一项关键技术。本设计采用Altera公司Cyclone系列的FPGA完成了对DDR SDRAM的控制,以状态机来描述对DDR SDRAM的各种时序操作,设计了DDR SDRAM的数据与命令接口。用控制核来简化对DDR SDRAM的操作,并采用自顶至下模块化的设计方法,将控制核嵌入到整个数据采集系统的控制模块中,完成了数据的高速采集、存储及上传。使用开发软件Quartus II中内嵌的逻辑分析仪SignalTap II对控制器的工作流程进行了验证和调试。最终采集到的

- 关键字:FPGADDR SDRAM数据采集

- 随着设计与制造技术的发展,集成电路设计从晶体管的集成发展到逻辑门的集成, 现在又发展到IP的集成,即SoC设计技术。SoC可以有效地降低电子信息系统产品的开发成本,缩短开发周期,提高产品的竞争力,是工业界将采用的最主要的产品开发方式。目前国内也加大了在SoC 设计以及IP 集成领域的研究。本文介绍的便是国家基金项目支持的龙芯SoC—ICT- E32 设计所集成的片上SDRAM 控制器模块设计与实现。 1 ICT-E32 体系结构 ICT-E32 是一款32位高性能SoC ,它集成龙芯1号

- 关键字:SoCSDRAM控制器MCU和嵌入式微处理器

- DDR3 SDRAM内存的总线速率达到600 Mbps to 1.6 Gbps (300 to 800 MHz),1.5V的低功耗工作电压,采用90nm制程达到2Gbits的高密度。这个架构毫无疑问更快、更大,每比特的功耗也更低,但是如何实现FPGA和DDR3 SDRAM DIMM条的接口设计呢? 关键字:均衡(leveling) 如果FPGA&nbs

- 关键字:FPGADDR3SDRAM接口模拟IC电源

- 在高速数字视频系统应用中,使用大容量存储器实现数据缓存是一个必不可少的环节。SDRAM就是经常用到的一种存储器。 但是,在主芯片与SDRAM之间产生的时序抖动问题阻碍了产品的大规模生产。在数字电视接收机的生产实际应用中,不同厂家的PCB板布线、PCB材料和时钟频率的不同,及SDRAM型号和器件一致性不同等原因,都会带来解码主芯片与SDRAM间访问时序的抖动问题。 本文利用C-NOVA公司数字电视MPEG-2解码芯片AVIA9700内置的SDRAM控制器所提供的时序补偿机制,设计了一个方便使

- 关键字:嵌入式系统单片机SDRAM时序控制MCU和嵌入式微处理器

- 引言 同步动态随机存储器(SDRAM),在同一个CPU时钟周期内即可完成数据的访问和刷新,其数据传输速度远远大于传统的数据存储器(DRAM),被广泛的应用于高速数据传输系统中。基于FPGA的SDRAM控制器,以其可靠性高、可移植性强、易于集成的特点,已逐渐取代了以往的专用控制器芯片而成为主流解决方案。然而,SDRAM复杂的控制逻辑和要求严格的时序,成为开发过程中困扰设计人员主要因素,进而降低了开发速度,而且大多数的基于FPGA的SDR

- 关键字:工业控制嵌入式系统单片机FPGASDRAM嵌入式工业控制

sdram介绍

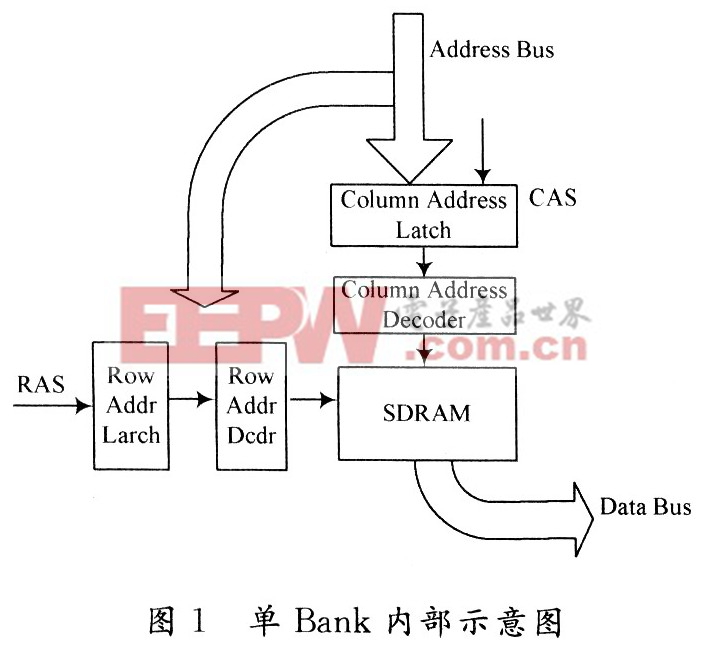

SDRAM:Synchronous Dynamic Random Access Memory,同步动态随机存取存储器,同步是指Memory工作需要同步时钟,内部的命令的发送与数据的传输都以它为基准;动态是指存储阵列需要不断的刷新来保证数据不丢失;随机是指数据不是线性依次存储,而是由指定地址进行数据读写。 SDRAM从发展到现在已经经历了四代,分别是:第一代SDR SDRAM,第二代DDR [

查看详细]

关于我们-

广告服务-

企业会员服务-

网站地图-

联系我们-

征稿-

友情链接-

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473