基于Xilinx V5的DDR2数据解析功能实现,摘要:介绍了一种基于Xilinx V5芯片的硬件板卡上,利用Verilog硬件编程语言,来实现DDR2对数据文件解析的目的:分析了CPCI总线与FPGA之间的通信特点;然后根据收到的数据文件要求,介绍了DDR2的使用方法;最后介绍了对

关键字:Xilinx Verilog DDR2 数据解析 信号波形

混合同余法产生随机噪声的FPGA实现,摘要:随着电子对抗技术的快速发展,在有源式干扰机中需要用到数字高斯白噪声。通过对混合同余法产生随机序列的原理研究,本文提出了一种利用FPGA产生高斯白噪声的方法。该方法在PC主控端的控制下,采用ROM查找表的方

关键字:高斯白噪声 混合同余法 FPGA Verilog HDL

可综合的意思是说所编写的代码可以对应成具体的电路,不可综合就是所写代码没有对应的电路结构,例如行为级语法就是一种不可综合的代码,通常用于写仿真测试文件。 建立可综合模型时,需注意以下几点: 不使用initial 不使用#10之类的延时语句 不使用循环次数不确定的循环语句,如forever,while等 不使用用户自定义原语(UDP元件) 尽量使用同步方式设计电路 用always块来描述组合逻辑时,应列出所有输入信号作为敏感信号列表,即always@(*) 所有的内部寄存器都应该能够被复

关键字:verilog FPGA

//基本D触发器 module D_EF(Q,D,CLK) input D,CLK; output Q; reg Q; //在always语句中被赋值的信号要声明为reg类型 寄存器定义 always @ (posedge CLK) //上升沿,下降沿用negedge表示,^_^ 需要记忆 begin Q <= D; end endm

关键字:D触发器 Verilog

这次我们讲一讲如何入门学习硬件描述语言和数字逻辑电路;学习数字逻辑电路,我推荐的一本书就是--《数字设计-原理与实践》,其他的深入点可以看看《完整数字设计》;而对于硬件描述语言呢?有两个原则,一个是买书的原则,一个是看书的原则。首先,你必须买两类书,一类是语法书,平常使用的时候可以查一查某些语法;一类是,对语言的使用的讲解和使用的方法(如何书写RTL,如何设计电路,如何调试代码,使用仿真器等);我用过一年的VHDL和两年的Verilog;作为过来人,我想介绍一些比较好的书给入门者,避免大家走弯路。

关键字:VHDL Verilog

这次我们讲一讲如何入门学习硬件描述语言和数字逻辑电路;学习数字逻辑电路,我推荐的一本书就是--《数字设计-原理与实践》,其他的深入点可以看看《完整数字设计》;而对于硬件描述语言呢?有两个原则,一个是买书的原则,一个是看书的原则。首先,你必须买两类书,一类是语法书,平常使用的时候可以查一查某些语法;一类是,对语言的使用的讲解和使用的方法(如何书写RTL,如何设计电路,如何调试代码,使用仿真器等);我用过一年的VHDL和两年的Verilog;作为过来人,我想介绍一些比较好的书给入门者,避免大家走弯路。

关键字:Verilog RTL

IC设计业界目前正研究如何统合Verilog-AMS与IEEE 1800标准的SystemVerilog,或导入模拟混合信号(AMS)成为新的SystemVerilog-AMS标准。 目前四大验证语言标准有Verilog-A与Verilog-AMS、VHDL-AMS、SystemC-AMS、SystemVerilog-AMS。其中以SystemVerilog-AMS为最新标准,但仍需数年研究才能供业界使用。 根据智财标准设立组织Accellera官网,许多研究正如火如荼进行,聚焦新功能与产

关键字:IC设计 Verilog

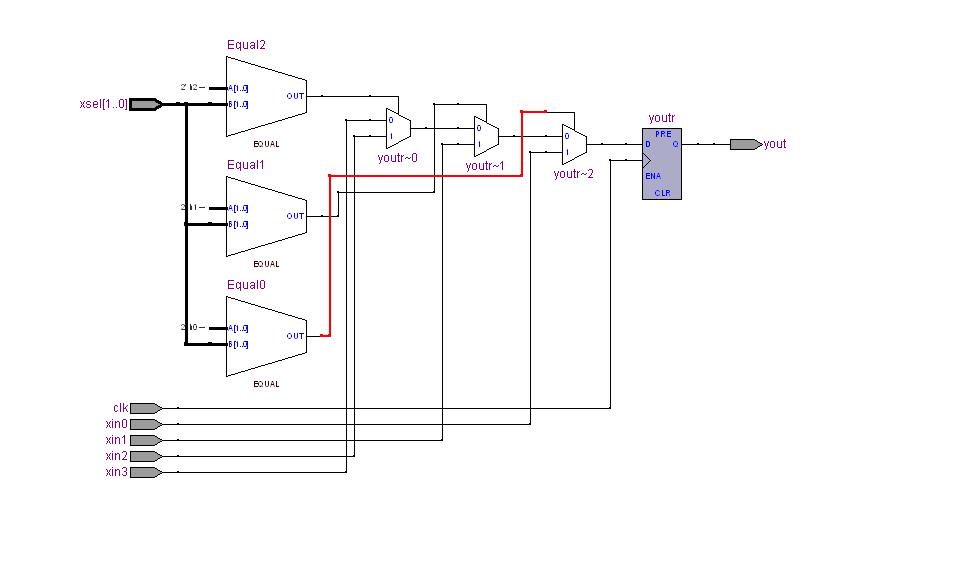

我们来做一个4选一的Mux的实验,首先是利用if…else语句来做,如下。 (由输入xsel来选择输出的路数xin0,xin1,xin2,xin3其一,输出yout) Ex3: input clk; input xin0,xin1,xin2,xin3; input[1:0] xsel; output yout; reg youtr; always @ (posedge clk) if(xsel == 2'b00) youtr <

关键字:verilog RTL

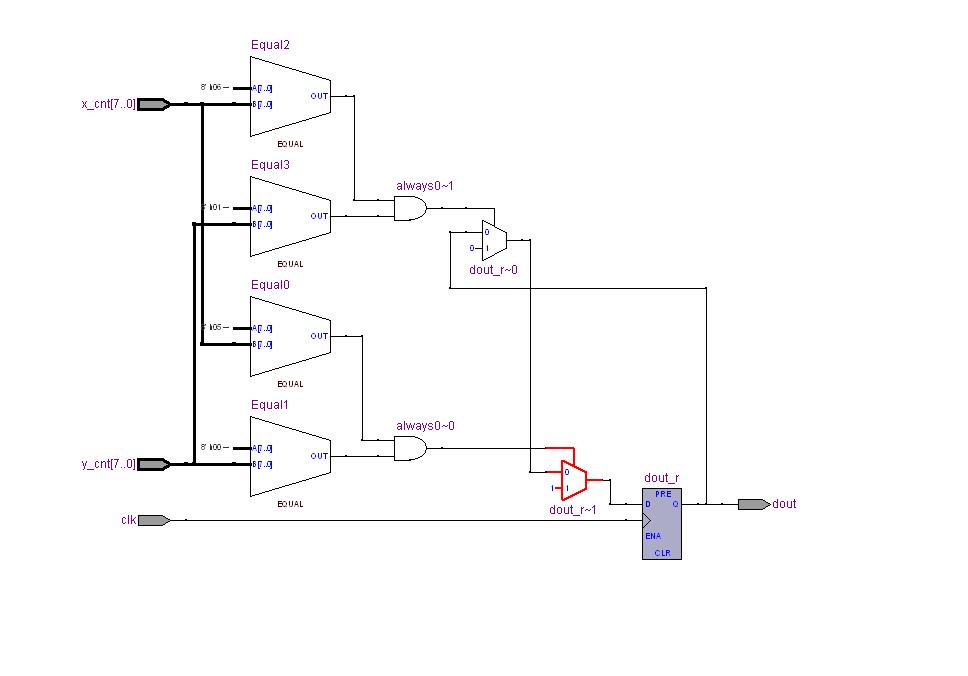

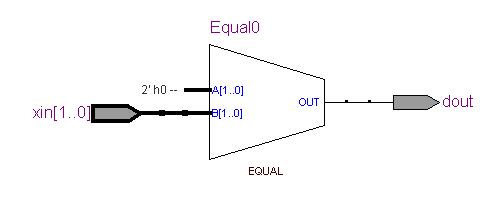

这次要说明的一个问题是我在做一个480*320液晶驱动的过程中遇到的,先看一个简单的对比,然后再讨论不迟。 这个程序是在我的液晶驱动设计中提取出来的。假设是x_cnt不断的增加,8bit的x_cnt加一个周期回到0后,y_cnt加1,如此循环,本意是要让下面的dout信号只有在x_cnt>=5 & y_cnt=0或者x_cnt<= 4,y_cnt=1这个区间内为1,其它时刻内为0。一般而言会有如下两种描述,前者是时序逻辑,后者是组合逻辑。当然除了下面两种编码风格外,还可以有很

关键字:verilog RTL

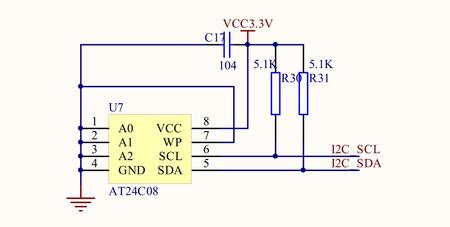

相信学过单片机的同学对I2C总线都不陌生吧,今天我们来学习怎么用verilog语言来实现它,并在FPGA学习版上显示。 i2c总线在近年来微电子通信控制领域广泛采用的一种新型的总线标准,他是同步通信的一种特殊方式,具有接口少,控制简单,器件封装形式小,通信速率高等优点。在主从通信中,可以有多个i2c总线器件同时接到i2c总线上,所有与i2c兼容的器件都有标准的接口,通过地址来识别通信对象,使他们可以经由i2c总线互相直接通信。 i2c总线由两条线控制,一条时钟线SCL,一条数据线SDA,这

关键字:FPGA i2c verilog

一、关于HDL 1. HDL简介 HDL : Hardware Discription Language 硬件描述语言,即描述FPGA/CPLD内部逻辑门的工作状态,来实现一定电路。 随着EDA技术的发展,使用硬件语言设计PLD/FPGA成为一种趋势。目前硬件描述语言有VHDL、Verilog、Superlog、System C、Cynlib C++、C Level等。 各种语言有各种优势,根据业界应用而定。 2. VHDL和Verilog区别 在业界,VHDL和Veri

关键字:FPGA Verilog

刚开始玩CPLD/FPGA开发板的时候使用的一块基于EPM240T100的板子,alter的这块芯片虽说功耗小体积小,但是资源还是很小的,你写点稍微复杂的程序,如果不注意coding style,很容易就溢出了。当时做一个三位数的解码基本就让我苦死了,对coding style的重要性也算是有一个比较深刻的认识了。 后来因为一直在玩xilinx的spartan3 xc3s400,这块芯片资源相当丰富,甚至于我在它里面缓存了一帧640*480*3/8BYTE的数据都没有问题(VGA显示用)。而最近

关键字:FPGA verilog RTL

学习FPGA其实也不算久,开始的时候参考别人的代码并不多,大多是自己写的,那时候做时序逻辑多一些。参加了中嵌的培训班,一个多月的时间在熟悉ISE软件的使用以及verilog语法方面下了苦功,也参考了不少书,算是为自己打下了比较好的基础。因为那时候培训的方向是软件无线电方面的,所以做了很多有关的模块程序,之前的日志里也发表了很多,关键是一个兴趣,感觉仿真后看到自己的一个个算法思想得到实现真有成就感。后来停了一段时间,因为实在没有比较有意思的活干了。 直到前段时间开始使用SP306的开发板,然后会参

关键字:FPGA verilog

图像传感器,或称感光元件,是一种将光学图像转换成电子信号的设备,它被广泛地应用在数码相机和其他电子光学设备中。早期的图像传感器采用模拟信号,如摄像管(video camera tube)。如今,图像传感器主要分为感光耦合元件(charge-coupled device, CCD)和互补式金属氧化物半导体有源像素传感器(CMOS Active pixel sensor)两种。本文介绍基于CMOS或CCD两种图像传感器的应用及技术文献,供大家参考。 基于USB传输及CMOS图像传感器的指纹识别仪的实

关键字:Verilog HDL QuartusⅡ VHDL

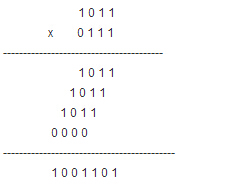

上次看了一下关于乘法器的Verilog代码,有几个地方一直很迷惑,相信很多初学者看这段代码一定跟我当初一样,看得一头雾水,在网上也有一些网友提问,说这段代码不好理解,今天小墨同学就和大家一起来看一下这段代码,我会亲自在草稿纸上演算,尽量把过程写的详细些,让更多的人了解乘法器的设计思路。 下面是一段16位乘法器的代码,大家可以先浏览一下,之后我再做详细解释 module mux16( clk,rst_n, start,ain,bin,yout,done ); inpu

关键字:FPGA Verilog 时序逻辑

verilog-xl介绍

您好,目前还没有人创建词条verilog-xl!

欢迎您创建该词条,阐述对verilog-xl的理解,并与今后在此搜索verilog-xl的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473