摘要:为降低设计成本,缩短设计周期,提出一种基于VHDL的洗衣机控制器的设计方案。该方案采用模块化的设计思想,并使用状态机完成控制模块的设计。整个系统在QuartusⅡ开发平台上完成设计、编译和仿真,并在FPGA硬件

关键字:洗衣机控制器 状态机 FPGA VHDL QuartusⅡ

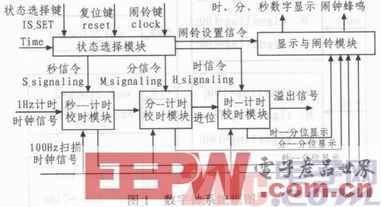

摘要:采用FPGA进行的数字电路设计具有更大的灵活性和通用性,已成为目前数字电路设计的主流方法之一。本文给出一种基于FPGA的数字钟设计方案。该方案采用VHDL设计底层模块,采用电路原理图设计顶层系统。整个系统在

关键字:EDA FPGA QuartusⅡ 数字钟

图像传感器,或称感光元件,是一种将光学图像转换成电子信号的设备,它被广泛地应用在数码相机和其他电子光学设备中。早期的图像传感器采用模拟信号,如摄像管(video camera tube)。如今,图像传感器主要分为感光耦合元件(charge-coupled device, CCD)和互补式金属氧化物半导体有源像素传感器(CMOS Active pixel sensor)两种。本文介绍基于CMOS或CCD两种图像传感器的应用及技术文献,供大家参考。 基于USB传输及CMOS图像传感器的指纹识别仪的实

关键字:Verilog HDL QuartusⅡ VHDL

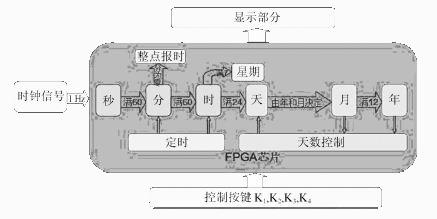

基于FPGA设计数字日历可以实现以软件方式设计硬件的目的,无需购买专用数字芯片,从而克服了传统利用多片数字集成电路设计数字日历存在焊接麻烦、调试繁琐、成本较高等问题。而且,基于FPGA的数字日历与传统系统相比,在设计灵活、开发速度、降低成本、计时精度、功能实现上都得到大幅度提升,能够更好地满足人们日常生活的需要。 本文介绍如何利用VHDL硬件描述语言设计一个具有年、月、日、星期、时、分、秒计时显示功能,时间调整功能和整点报时功能的数字日历。在QuartusⅡ开发环境下,采用自顶向下的设计方法,建

关键字:FPGA QuartusⅡ

摘要:采用FPGA进行的数字电路设计具有更大的灵活性和通用性,已成为目前数字电路设计的主流方法之一。本文给出一种基于FPGA的数字钟设计方案。该方案采用VHDL设计底层模块,采用电路原理图设计顶层系统。整个系统在QuartusⅡ开发平台上完成设计、编译和仿真,并在FPGA硬件实验箱上进行测试。测试结果表明该设计方案切实可行。 EDA(Electronic Design Automation)又名电子设计自动化,其基本特征是:以超大规模可编程逻辑器件,如FPGA,为设计载体,以硬件描述语言,如VHDL,为

关键字:FPGA QuartusⅡ

针对实现传统模糊PID控制器时,需要建立比例、积分和微分三个模糊控制器,存在模糊规则较繁杂、运算量大、速度慢等问题,提出了以PD模糊控制器代替P1模糊控制器,采用两个PD模糊控制器,并引入FPGA技术,实现模糊PID控制器。通过QuartusⅡ和Matlab联合仿真,比较了基于FBC和SBC实现的模糊PID控制器的控制效果,验证了设计方案的正确性和可行性。

关键字:模糊PID 控制器 FPGA:QuartusⅡ Matlab

1 引言 随着FPGA向低成本、低功耗、高性能方向发展,其I/O引脚大多采用微间距TOFP或BGA封装工艺,因而使引出多种内部信号的I/O引脚以及FPGA的验证工作变得非常困难,同时FPGA的验证和调试耗时占总开发时间的50%以上。 在验证和调试系统时,传统上是把信号线引到I/O引脚,然后采用示波器、逻辑分析仪或总线分析仪进行测量和分析。由于这些设备相当昂贵,而且调试时又需要许多连线夹,因此一不小心就会烧坏器件或电路板。 伴随着EDA 工具的快速发展,Altera公司在Quartus

关键字:FPGA I/O EDA QuartusⅡ 存储

电子产品世界,为电子工程师提供全面的电子产品信息和行业解决方案,是电子工程师的技术中心和交流中心,是电子产品的市场中心,EEPW 20年的品牌历史,是电子工程师的网络家园

关键字:DSP FPGA FIR QuartusⅡ

quartusⅡ介绍

您好,目前还没有人创建词条quartusⅡ!

欢迎您创建该词条,阐述对quartusⅡ的理解,并与今后在此搜索quartusⅡ的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473