半导体业界的HKMG攻防战:详解两大工艺流派之争

在IEDM2009 会议上,高通公司的高管曾表示他们很支持台积电去年七月份宣布将启用Gate-last工艺的决定。而今年1月份,高通则宣布已经与 GlobalFoundries公司签订了28nm制程产品的代工协议。这样,届时人们便有机会可以实际对比一下分别来自台积电和 GlobalFoundries两家公司,分别使用gate-last与gate-first两种工艺制作出的手机芯片产品在性能方面究竟有多大的区别。目前,高通公司的40nm制程手机用处理器类属与高性能芯片,其运行频率达到了1GHz,不过其功耗也控制得相当好,在谷歌Android智能手机中有使用这种处理器产品。

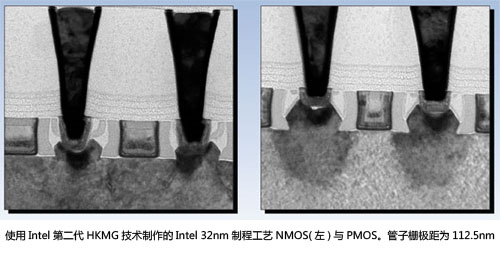

Intel公司的制程技术高管Mark Bohr则表示Intel公司的Atom SOC芯片还需要一年左右的时间才会启用32nm制程工艺。当被问及应用gate-last工艺以后为什么芯片的核心尺寸会有所增大,是不是由于 gate-last本身的限制,导致更改后的电路设计方案管芯密度有所下降的问题时,Bohr表示Intel公司45nm gate-lastHKMG制程产品上电路设计方案的变动并不是由于应用了gate-last所导致,而是与当时Intel在45nm制程产品上还在继续使用干式光刻技术有关。他表示“当时之所以会采用那种核心面积较大的设计规则,其目的并不是为了满足Gate-lastHKMG工艺的要求,而是要满足使用干式光刻技术的要求。”(Intel在45nm制程节点仍然在使用干式光刻技术,直到32nm才开始使用沉浸式光刻技术。)

HKMG技术未来一段时间内的发展趋势:

High-k绝缘层的材料选择方面,包括Intel公司的Bohr在内,大家似乎都同意HfO2将在未来一段时间内继续被用作High-K层的材料,业界近期将继续在改良HfO2材料上做文章,部分厂商可能还会考虑往HfO2层中添加一些特殊的材料,但他们近期不会把主要的精力放在开发介电常数更高的材料方面。

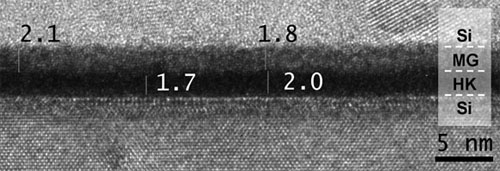

另外,有部分厂商的主要精力则会放在如何减小High-k层下面的SiO2界面层(IL)的厚度方面,其目标是在High-k绝缘层的等效氧化物厚度为10埃时能把这种界面层的厚度降低到5埃左右。Sematech公司负责High-k项目研究的高管Paul Kirsch表示:“业内现在考虑较多的主要是如何进一步优化HfO2材料,而不是再花上五年去开发一种新的High-k材料。从开发时间要求和有效性要求方面考虑,目前最有意义的思路是考虑如何消除SiO2界面层和改善High-K绝缘层的介电常数值。”

Gatefirst在如何有效消除SiO2界面层(ZIL)方面的优势及各方评述:

消除SiO2界面层方面,在去年12月份举办的IEDM会议上,科学家们发布了多篇有关如何消除SiO2界面层的文章(ZIL:zero interface layer),其中IBM的Fishkill技术联盟也公布了自己的方案,并宣称这种方案将在自己的gate-first 32/28nm制程中使用。

评论