半导体业界的HKMG攻防战:详解两大工艺流派之争

专家意见:

本文引用地址://m.amcfsurvey.com/article/107122.htmGartner公司的半导体产业分析师Dean Freeman表示:“台积电转向Gate-last,说明这种工艺在性能方面还是存在一定的优越性的。虽然Gate-first工艺制成的产品在管芯密度方面 较有优势,但继续应用这种工艺一定存在一些台积电无法克服的难题。”

欧洲校际微电子中心组织IMEC负责high-k技术研发的主管Thomas Hoffmann曾经在IEDM2009大会上指出了Gate-first工艺在性能方面存在的不足,不过在会后的一次访谈中,他表示尽管Gate- first存在一些性能方面的缺点,但是对一部分对性能并不十分敏感的第功耗器件还是能够满足要求的。

他表示:“对瑞萨等开发低功耗器件的公司而言,也许Gate-first工艺是目前较好的选择。这类器件一般对Vt值和管子的性能并没有太高的要求。不过当产品的制程节点发展到28nm以上级别时,这些公司便需要转向Gate-last。”不过”对以追求性能为主的厂商而言,Gate-last则是必然之选。IBM的产品显然属于这种类型,所以我认为如果他们不使用Gate-last的话,就必须在如何降低Vt的问题上想出好办法。当然这种方案的复杂性会更大,而且还有可能会影响到产品的良率。而最终他们也有可能会倒向Gate-last工艺,这就是IBM Fishkill生产技术联盟中的伙伴感到担心的地方。“

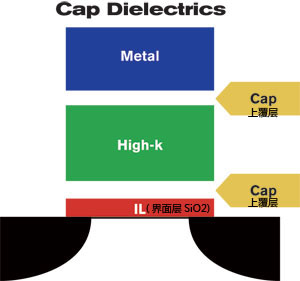

Gate-first工艺控制管子门限电压的方案和难点所在:上覆层(Cap layer):

据Hoffmann介绍,尽管在Gate-last工艺中,制造商在蚀刻和化学抛光(CMP)工步会遇到一些难题,但是Gate-first工艺也并非省油的灯。如前所述,目前Gate-first工艺虽然不好控制Vt,但也不是完全没有办法,其主要的手段是通过设置 一定厚度的high-k绝缘体上覆层(cap layer)来实现,这种方案需要在high-k层的上下位置沉积氧化物薄层。比如在NMOS管中,便需要在high-k层的上部沉积一层厚度小于1nm的 La2O3薄层,以达到调整Vt电压的目的;而在PMOS管中,则需要通过蚀刻工步将这一层薄层去掉,换成 Al2O3材质的薄层,这样便需要复杂的工艺来控制如何在PMOS管中将这一薄层去掉而不影响到NMOS的上覆层。

他表示:”NMOS管的上覆层需要采用La2O3材料制作,而PMOS管则需要用Al2O3来制作上覆层,这样就需要在NMOS管的上覆层上覆盖一层光阻胶,然后再用显影+蚀刻方式去掉沉积在PMOS管中的La2O3,不过处理完成之后要除去覆盖在厚度小于1nm的La2O3 上覆层上的光阻胶时,由于上覆层的厚度极薄,因此如果不能小心控制就会对上覆层造成一定的损坏,这就要求厂商具备非常高超精密的去胶工艺。“

Gate-last的优势:可自由设置和调配栅电极材料的功函数值,充分控制Vt电压

ASM公司的外延产品和ALD(原子层淀积)业务部经理Glen Wilk则表示业内已经就gate-first与gate-last之间在性能,复杂程度和成本方面的优劣对比争执了许久,”不过我认为随着产品制程尺寸的进一步缩小,gate-last工艺的优越性开始逐步体现,由于这种工艺的栅极不必经受高温工步,因此厂商可以更加自由地设置和调配栅电极材料的功函数值,并很好地控制住管子的Vt电压。”

Wilk表示,随着制程尺寸的进一步缩小,采用 gate-first工艺的厂商会发现“PMOS管的特性越来越难控制,实施Gate-first工艺的难度也悦来越大,因此我认为未来业界对gate- last工艺的关注程度会越来越广泛。”Wilk认为,由于gate-last工艺可以很好地控制栅极材料的功函数,而且还能为PMOS管的沟道提供有利改善沟道载流子流动性的硅应变力,因此gate-last工艺将非常适合低功耗,高性能产品使用,他表示:“不过我认为内存芯片厂商可能在转向gate-last工艺时的步伐可能会稍慢一些,他们可能会在未来一段时间内继续使用gate- first工艺,不过gate-last工艺显然有助于提升产品的性能和降低产品的待机功耗。”

而 Applied Materials公司的CTO Hans Stork则表示gate-first工艺需要小心对待用来控制Vt电压的上覆层的蚀刻工步,而gate-last工艺则需要在金属淀积和化学抛光工步加以注意。“长远地看,我认为Gate-last工艺的前景更好一些。”他表示芯片厂商目前都非常关注Intel 公司的32nm制程SOC芯片工艺,在这种工艺中,high-k绝缘层的等效氧化物厚度(EOT)为0.95nm.他说:“Intel将其32nm gate-last制程SOC芯片产品的应用范围从高性能应用市场进一步拓展到了低漏电/低电压应用领域,而手机芯片则正好需要具备这些特性。”客户们对 gate-last和gate-first工艺在工函数控制,成本,产能,良品率等方面的实际对比数据非常关注。以至于已经有部分手机芯片厂商如高通等已经开始要求代工商能为他们提供“能与Intel的产品性能相近”的产品。

评论