基于DSP的高性能通用并行弹载计算机设计与实现

摘要:为满足弹上信号处理领域不断增长的任务需求并适应不同的应用场合,设计高性能通用并行计算机,进而构建各类信号处理系统是一种趋势。基于时共享总线和分布式两种并行结构的理论分析,结合信号处理系统的特点,设计了一种高性能通用并行弹载计算机,它具有标准化、模块化、可扩展、可重构、混合并行模式、多层次互联的特性,通过构建典型弹载计算机验证了这些特性。

关键词:弹载计算机;并行处理;TS201;FPGA

0 引 言

随着技术的发展,在导弹控制和通信等领域,需要处理的任务规模越来越大。虽然随着VLSI技术的发展,已产生了运算能力达每秒几十亿次的处理器,但还远远不能满足这些领域的需求。而VLSI技术的发展已受到其开关速度的限制,进一步提高处理器主频遇到的困难越来越大。为此,把用于大型计算机的并行处理技术应用到信号处理中来,在信号处理系统中引入并行多处理器技术是必然趋势。传统弹载计算机一般针对特定场合,先确定算法,再根据算法确定系统结构,由于系统结构与算法严格相关,因此通用性较差。随着一些标准技术(标准板型、接口、互联协议等)在弹上控制系统中的应用,设计标准化、模块化的通用型计算机成为了可行。而且所设计的还要可扩展、可重构,进而根据不同的应用场合和算法构建各种弹载计算机系统。

1 并行弹载计算机处理结构模型

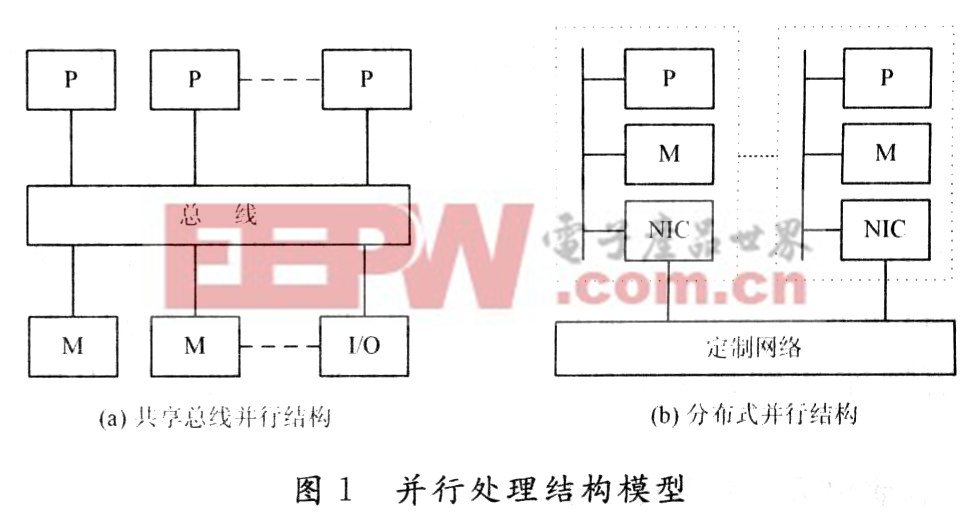

普遍的两种并行处理结构如图1所示,一种是共享总线结构,另一种是分布式并行结构。其中,P(Proces-sor):处理器;M(Memory):存储器;MB(Memory Bus):存储器总线;NIC(Network Interface Circuitry):网络接口电路。共享总线结构中多个处理器P经由高速总线连向共享存储器,每个处理器等同地访问共享存储器、I/O设备和操作系统服务。分布式并行结构中多个处理节点通过高通信带宽、低延迟的定制网络互联,每个处理节点都有物理上的分布存储器,节点间通过消息传递相互作用。

并行处理的目的是采用多个处理器同时对任务处理,从而减小任务执行时间,它主要反映在加速比(S)和并行效率(E)上。加速比是指对于一个特定应用,并行算法的执行速度相对串行算法加快了很多倍。效率则是针对每个处理器来衡量的。依据并行处理中可扩放性(Sealability)评测的等效率度量标准可从理论上评测这两种结构。

评论