音频信号数字化光纤传输实验仪信道的设计与实现

2.3.2 A/D转换部分

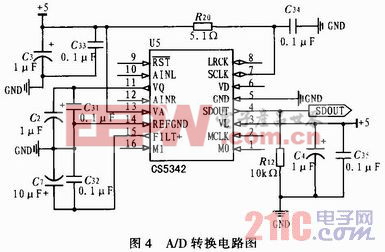

模数转换电路采用了Cirrus Logic公司出品的专业音频处理集成芯片CS5342,其工作时钟频率设定为18.432 MHz,由FPGA提供。信号由AINL和AINR管脚输入,SDOUT输出转换后的串行二进制数据,LRCK和SCLK输出采样频率。M0和M1脚分别接高、低电平,以保证芯片工作在双倍速主动模式上,分频产生采样频率96 MHz。另外,RST脚置高电平,各类参考电压引脚加入适当的滤波电容,使芯片稳定且正确地工作。其电路如图4所示。本文引用地址://m.amcfsurvey.com/article/154036.htm

2.4信号发送部分

由FPGA处理后的数据要通过光纤发送,需先将并行数据转换为串行数据,再将串行数据转换为光信号。

2.4.1 并/串转换

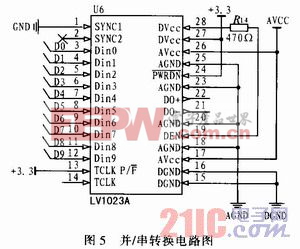

电路采用串化器SN65LV1023A集成芯片实现,电路如图5所示,其对应接收端由解串器SN65LV1224A集成芯片完成。SN65LV1023A可以将10位并行数据转换为串行差分数据流,该差分数据流可以由SN65LV1224A还原为10位的并行数据。这一组芯片内部有锁相环,可以为数据输出自己匹配时钟。串化器SN65LV1023A参考时钟选为18.432MHz与数据在该时钟频率下输入,其芯片内部匹配产生数据输出时钟,每一个10位并行数据转换为12位串行数据,其中多出一个起始位和一个终止位,所以有效频率为184.32 MHz。解串器的参考时钟也定为18.432 MHz,以满足数据传输需求。

由于音频信号是实时不断的,所产生的数据流连续进行,所以电路不能设置进入高阻态或省电模式,因此LV1023的DEN和PWRDN都置高电位。

串行数据的准确传输需要串化器和解串器同步,该组芯片采用的是随机同步方式。串化器的SYNC1和SYNC2悬空。解串器的LOCK输入到FP GA以对数据传输进行实施控制。

数字通信相关文章:数字通信原理

评论