音频信号数字化光纤传输实验仪信道的设计与实现

3 软件设计及仿真介绍

系统采用VerilogHDL语言进行程序编写,在QuartusⅡ环境下编辑仿真。FPGA内部时钟由18.432 MHz的有源晶振提供。FPGA的工作是:

1)提供D/A转换芯片CS4334,A/D转换芯片CS5342,并串转换芯片LV1023的工作时钟和串并转换芯片LV1224的参考时钟,其值均为18.432 MHz。

2)发送端对数据进行8B10B编码,并将转换后的数据传送给串化器;接收端获取串并转换后的十位数据,进行解码,还原为编码前的八位数据,并将解码后的数据传送给数模转换芯片。

3.1 8B10B编解码

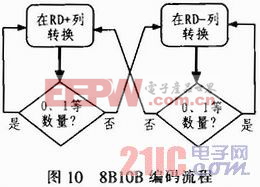

8B10B编码是目前高速串行通讯普遍采用的编码方式,8B10B编码的目的是将八位数据转换成10位的数据,并使转换后的数据流中“0”和“1”的数量平衡,避免发送过程中因过多重复的出现“0”或“1”而发生的错误,提高线路传输的性能,有利于接收器更准确的捕捉同步时钟,而且采用特定的码元可以使接受端更准确地对准码元。8B10B编码可以看成是586B和384B编码的组合,组合过后有些编码可能有两个值,“1”和“0”的差值称为平衡度,用RD-表示平衡度为+2或0,RD+表示平衡度-2或0。将转换后的数据按平衡度分为RD-和RD+两列。设变量DISPIN表示正在转换的数的平衡度,DISPOUT表示下一个转换的数的平衡度。初始时设DISPIN与DISPOUT相等,先从RD-中开始转换,如果转换后的数“0”和“1”的数量相等,继续在RD-列中转换下一个数,如果“0”和“1”的数不等,则转到RD+列中转换。同理在RD+列中,如果“0”、“1”个数相等则继续在RD+中,否则换到RD-中。本文引用地址://m.amcfsurvey.com/article/154036.htm

解码部分将10位数据的前六位和后四位分别按照5B6B和3B4B的列表解码即可。

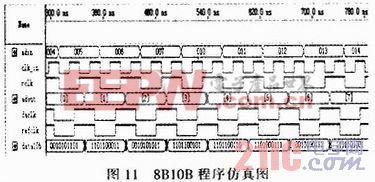

3.2 仿真

设计程序经QuartusⅡ综合器编译综合成功后,可以对输入数据、中间产生的数据、输出数据进行仿真。装置采用的8B10B编码方式,分为3B4B和5B6B进行编码。解码部分依照编码时相同的分发将十位数据分为4B和6B分别解码。解码后再按顺序组合成8位数据。程序以4B3B、6B5B分别查表的方式实现。程序仿真图中,adin是编码之前的八位数据,设为逐次加一的计数数据,为了方便比较,图中用十进制表示。编码后的十位数据为data10b,adout是解码后的数据。可以看到虽有延迟,解码后数据仍为计数数据,因此程序可以准确地实现解码功能。

4 结束语

综合以上设计的电路模块,其基本功能实现了音频信号的采集与数字化处理,并用光纤完成音频数字信号的传输过程,其信号通道研制完成,为整套实验装置的设计研制奠定了基础保证,它是系统的核心关键部分。

作为大学基础实验领域研发的新型实验仪器,不管是设计研制者,还是通过其实验教学的应用者都在其工作与实验的实践中,学习掌握和了解多方面的专业理论与技术知识:1)认识模拟电路、数字电路、模数和数模转换等电子电路知识,了解印刷电路板设计方法;2)了解可编程逻辑器件的基本原理、硬件设计、软件编程、仿真调试与使用工作方法;3)了解模拟信号与数字信号的区别与特点,掌握二者之间对应

关系及转换原理;4)了解音频信号构成、处理及传输过程,以及并/串、串/并转换的原理及同步工作方法;5)了解光/电和光/电转换专业知识与当代应用技术;6)学习和了解模拟信号与数字信号光纤传输过程等现代电子专业理论与应用技术。

数字通信相关文章:数字通信原理

评论