ASIC后端设计中的时钟树综合

摘要:时钟树综合是当今集成电路设计中的重要环节,因此在FFT处理器芯片的版图设计过程中,为了达到良好的布局效果,采用时序驱动布局,同时限制了布局密度;为了使时钟偏移尽可能少,采用了时钟树自动综合和手动修改相结合的优化方法,并提出了关于时钟树约束文件的设置、buffer的选型及手动修改时钟树的策略,最终完成了FFT处理器芯片的时钟树综合并满足了设计要求。

关键词:FFT处理器芯片;布局布线;时钟树综合;时钟偏移

0 引言

在大规模高性能的ASIC设计中,对时钟偏移(Clock Skew)的要求越来越严格,时钟偏移是限制系统时钟频率的主要因素。而时钟树综合又是减小时钟偏移的有效途径,因此它是ASIC后端设计中最重要的环节之一。本文以基于SOC Encounter,采用SMIC0.18μm工艺进行的FFT处理器的版图设计为例,提出在设计过程中如何减小时钟偏移,结合手动优化帮助工具设计出更好的时钟树。

1 时钟偏移产生的原因分析

同一时钟源到达各个同步单元的最大时间差称作时钟偏移。产生时钟偏移的原因有:时钟源到各个时钟端点的路径长度不同;各个端点负载不同;在时钟网中插入的缓冲器不同等。时钟偏差过大会引起同步电路功能混乱。

在图1中,假设CLK到达reg1和reg2的时间差最大,为dskew,组合逻辑C的延时为dc,寄存器的延时为d,其建立时间约束为dsetup,保持时间为dhold,时钟周期为T。满足建立时间的要求是在CLK2跳变前的dsetup时间,reg2上D端的数据应该稳定,考虑最坏情况reg1比reg2晚dskew,这时满足的时间关系应该是:

![]()

满足保持时间的要求是:在CLK2跳变后的dhold时间内,reg2上D端的数据必须保持稳定,考虑最坏情况reg1比reg2早dskew,这时满足的时间关系应该是:

![]()

由此可见,时钟偏移对电路速度和时钟频率的限制是很大的,而寄存器的保持时间、建立时间和自身的延时,都是与器件单元本身的结构和性质有关,依赖于工艺的改进来进一步减小,所以减小skew成为后端设计重要内容,也是提高电路速度的关键。

2 SOC Encounter的时钟树综合

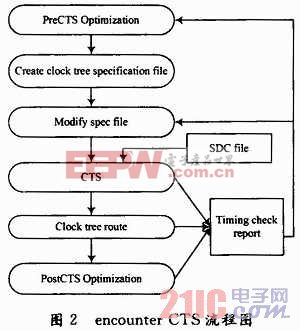

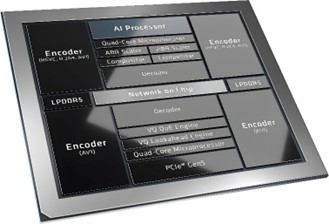

SOC Encounter的时钟树综合在完成布局之后进行,可以采用手动模式和自动模式。手动模式能控制时钟树的层次、buffer的数目和每层加入buffer的类型。自动模式根据时钟树定义文件自动决定时钟树的层次和buffer的数目。时钟树综合从外部时钟输入端口自动遍历整个时钟树,遍历完成后加入buffer用来平衡时钟树。SOC Encounter的时钟树综合流程如图2所示。

评论