三星投入DRAM 18nm制程研发

2016年三星电子(Samsung Electronics)于DRAM将以开发18奈米制程为其投资重点,DIGITIMES Research观察,为克服DRAM18奈米制程微缩所面临的电容器(Capacitor)易倒塌、杂讯(Noise)增加、电荷外泄及曝光显影变复杂等课题,三星将运用四重曝光显影技术 (Quadruple Patterning Technology;QPT)与超微细导电膜形成技术,以维持其在DRAM技术的领先地位。

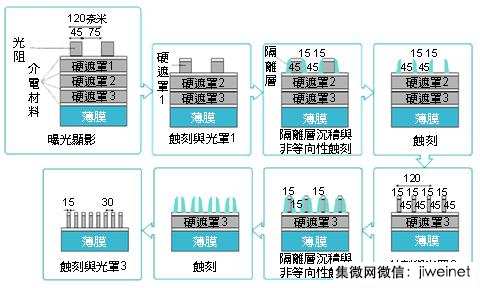

本文引用地址://m.amcfsurvey.com/article/201605/291147.htm三 星于DRAM18奈米制程将运用自动对位QPT(Self Aligned QPT;SaQPT)方式,系自动对位双重曝光显影技术(Self Aligned Double Patterning Technology;SaDPT)的延伸,亦即进行两次SaDPT,以达成不需增加光罩数的理想。

不过,三星所采SaQPT仍需形成超 微细导电膜,故需追加原子层沉积(Atomic Layer Deposition;ALD)制程,及形成图案所需的蚀刻与化学机械研磨(Chemical Mechanical Polishing;CMP)等制程,使得三星所采SaQPT成本将为单次曝光显影技术的3.3倍。

在超微细导电膜方面,由于以往系采用 分子单位的物质,来蒸镀导电膜,然因分子单位下的粒子较大,不易形成均匀薄膜,为避免电子外泄,需蒸镀较厚的导电膜,然此将导致电容器内的电荷储存量减 少,三星改用原子物质来制作导电膜,可望克服此一问题,推动DRAM朝18奈米制程微缩。

四重曝光显影技术的主要制造流程

资料来源:DIGITIMES整理,2016/4

评论