采用FPGA通过BT.656接口实现传输4路视频流的方法

引言

itu-r bt.656定义了一个并行的硬件接口用来传送一路4:2:2的ycbcr的数字视频流。视频流的分辨率为720×576像素的d1格式。我们需要发送的视频数据源通常是经过mpeg2压缩的,分辨率为352×288像素的cif格式。在输出到显示终端前,处理器需要对cif格式的图像数据插值为d1(720×576像素)格式,然后再通过itu-r bt.656并行的硬件接口输出给视频编码器。在这种前提下,可以利用一个itu-r bt.656的硬件接口传输4路不同的cif格式的视频数据流,然后在接收侧通过fpga(现场可编程门阵列)将4路视频数据流分离、插值生成d1格式的数据输出给视频编码器。通过该方式,可以克服某些视频处理器输出端口的限制,使视频输出端口扩展为原来的4倍。同时,由于使用fpga进行插值运算,分担了一部分视频处理器的工作量。

本文引用地址://m.amcfsurvey.com/article/21012.htm1 硬件连接

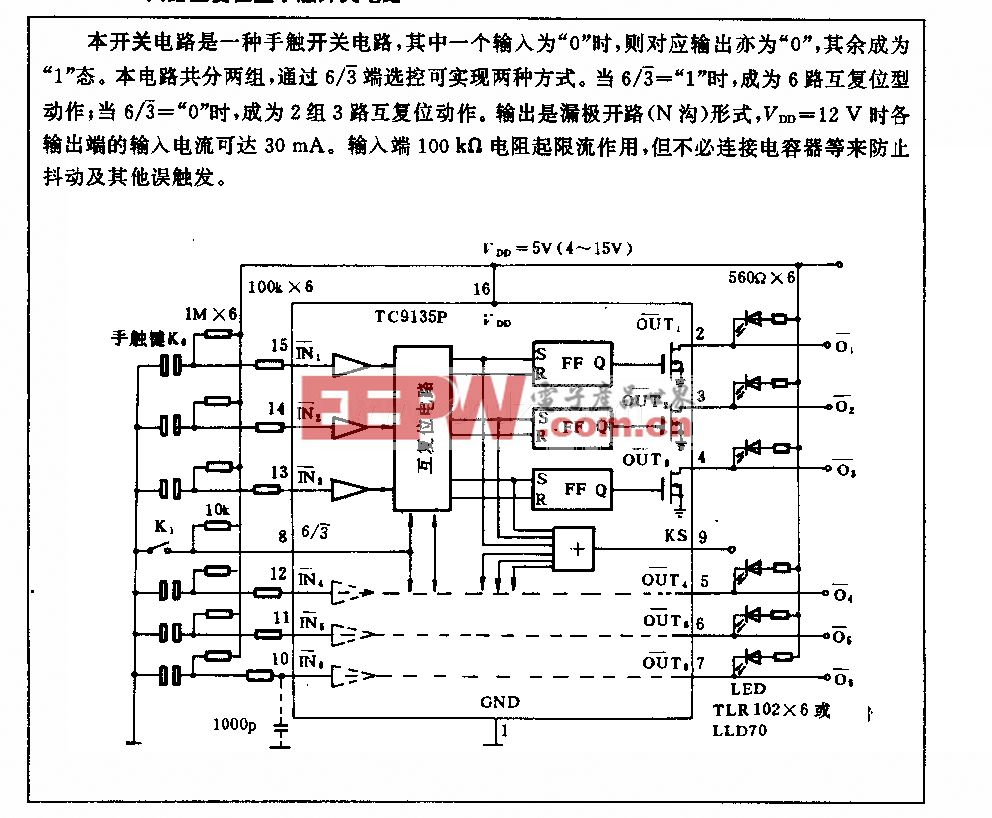

图1展示了一个bt.656并行硬件接口用来连接一个视频处理器和视频编码器的情况。该硬件接口由8根数据信号和1根时钟信号组成。

图2所示是通过fpga扩展4路视频的连接方式。fpga通过bt.656接口接收视频处理器发出的数据信号,然后将4路视频信号分离、插值后通过4路bt.656并行硬件接口输出到4个视频编码器,实现视频处理器一个视频输出端口同时输出4路视频信号。

2 数据结构

2.1 标准bt.656并行数据结构

bt.656并行接口除了传输4:2:2的ycbcr视频数据流外,还有行、列同步所用的控制信号。如图3所示,一帧图像数据由一个625行、每行1 728字节的数据块组成。其中,23~311行是偶数场视频数据,336~624行是奇数场视频数据,其余为垂直控制信号。

bt.656每行的数据结构如图4所示。

图4中,每行数据包含水平控制信号和ycbcr。视频数据信号。视频数据信号排列顺序为cb-y-cr-y。每行开始的288字节为行控制信号,开始的4字节为eav信号(有效视频结束),紧接着280个固定填充数据,最后是4字节的sav信号(有效视频起始)。

sav和eav信号有3字节的前导:ff、ff、00;最后1字节xy表示该行位于整个数据帧的位置及如何区分sav、eav。xy字节各比特位含义见图5。

图5中,最高位bit7为固定数据1;f=0表示偶数场,f=1表示奇数场;v=0表示该行为有效视频数据,v=1表示该行没有有效视频数据;h=0表示为sav信号,h=1表示为eav信号;p3~p0为保护信号,由f、v、h信号计算生成;p3=v异或h;p2=f异或h;p1=f异或v;p0=f异或v异或h。

2.2 使用bt.656并行接口传输4路cif格式视频的数据结构

视频处理器的输出是灵活多变的,可以改变处理器的输出数据结构来同时传送4路252×288像素的视频信号。bt.656并行接口传输的有效视频数据流为720×586,正好可以分割为4个360×288像素的空间来传输4路352×288像素的视频数据。多余的空间用固定数据“8010”进行填充。

修改后的数据结构如图6所示。

原来存放第1场的数据的位置用来存放第1、第2路视频数据;原来存放第2场的数据的位置用来存放第3、第4路视频数据。

3 fpga实现的功能

fpga主要用来完成4路352×288像素视频流的分离,以及将视频流插值到标准bt.656接口所需的720×586像素的分辨率。同时,该fpga还要重新生成sav、eav帧控制信号,结合插值后的4路视频流产生新的符合bt.656结构的数据帧传送给视频编码设备。其功能框图如图7所示。

首先,4路352×288像素的视频流从bt.656结构的帧结构中分离出来,分别存储到各自的存储空间。然后,352×288像素的视频流被读取、插值为704×288像素,然后再填充为720×288像素的视频流。在成帧的模块中,产生bt.656的帧结构所需的sav、eav信号;将插值生成的720×288像素的数据作为偶数场的数据填入bt.656的帧结构中,奇数场的数据复制偶数场的数据。最后,将生成的bt.656标准视频流发送给视频编码器输出到显示终端上。

3.1 存储器选择

由于需要同时存储4路352×288的视频流,需要的存储空间为4路×288行×352×2字节(视频流为4:2:2的ycbcr信号,一个点通过亮度信号和色差信号来表示,所以图像的一个点实际占用2字节)。计算可得需要800 kb左右的空间。低成本的fpga内部很难提供如此多的存储空间,可以外挂一片1mb容量的sram用于存储视频数据。

bt.656接口定义的时钟频率为27 mhz。sram要能提供1路8 bit×27 mhz数据写入,4路8bit×27 mhz读出,总共1gbit/s以上的数据带宽。可以选择位宽为16 bit、工作时钟频率100 mhz、带宽为1.6gbit/s的sram。

3.2 插值算法

将352×288像素的原始视频流变换为714×288像素的视频流就需要进行插值。该插值运算是一维的,也就是说只需要加倍每行的点数而行数不变。插值运算前,应该先将y、cb、cr信号分离,然后分别对y、cb、cr信号进行插值。简单的插值法有最近邻域法和线性插值法等。最近邻域法是插入点的值简单复制邻近点的值;线性插值法是插入点相邻的两个数据取算术平均值,得到插入值。应用更加复杂的插值算法可以改善图像质量。在本文设计中,实现这两种简单的插值方法就已经满足需求。

4 结束语

本文提出一种利用一个bt.656接口传输4路视频流的方法。该方法利用fpga接收4路cif格式的视频数据,然后分离、插值为4路d1格式视频流后,重新生成bt.656的数据帧发送给视频编码芯片,从而实现视频处理器的一个硬件接口传输4路视频图像。通过该方法可以克服视频处理器芯片输出端口的限制,增加了其扩展性。在实际测试和应用中,取得了满意的效果。

评论