Intel 10nm工艺将使用量子井场效电晶体及新型半导体材料

Intel前几天庆祝了半导体业界黄金法则——摩尔定律,通过更先进的工艺不断提升电晶体密度是Intel取胜的关键,他们也以此维护了摩尔定律的准确。如今Intel的制造工艺已经是14nm,下一步就是10nm工艺,面临的挑战还会更多,Intel实际上也延期了10nm工艺进程,但Intel手中的外星科技可不少,分析认为Intel将在10nm工艺启用量子井场效电晶体(Quantum Well FET,简称QWFET),还会使用铟镓砷及应变锗两种新型半导体材料。

本文引用地址://m.amcfsurvey.com/article/273219.htm

如今的集成电路基本上都是基于矽基材料,电晶体的性能、运行电压及电流都与电晶体的结构有关,因此整体功耗密度相同的情况下,电晶体的功耗与电压的成正比——当然,电晶体密度是在不断提升到的(这是摩尔定律的内容)。这个规律是1975年IBM公司的研究人员Robert Dennard总结的,因此这个定律也以他的名字命名——这就是Dennard scaling定律的来源。

这些其实是本文内容的前奏,这个定律在公园2000年前都是适用的,但2005年David Wang在IEDM会议上提出,电晶体的性能不能再通过几何结构而提升,功耗问题越来越严重,而功耗来源于两个方面——渗漏电流带来的静态功耗以及电晶体开关带来的动态功耗(注:动态功耗有个公式Switching power = C*V2*F)。

现在的情况就是电晶体越小,渗漏电流越来越严重,解决功耗问题的重点就转移到渗漏电流这方面来了,Intel曾经在90nm工艺使用应变矽工艺,45nm节点使用HKMG(高K金属闸极)工艺,22nm工艺使用FinFET电晶体工艺,这都有助于降低渗漏电流,进而降低功耗。

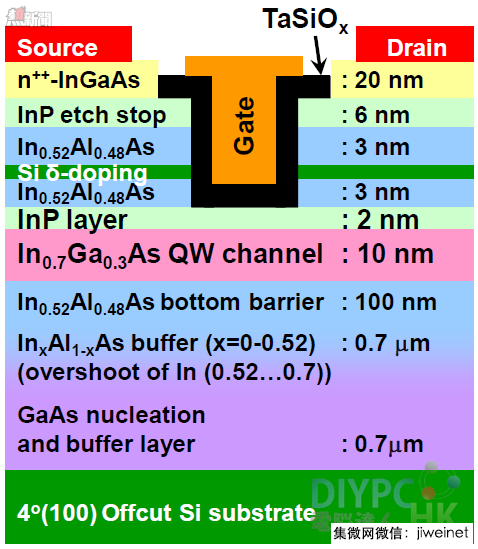

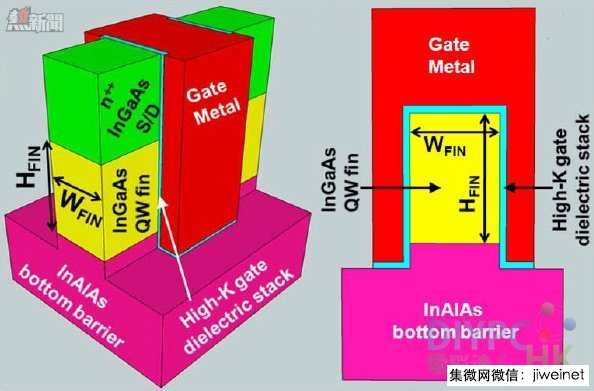

分析师 David Kanter认为Intel有很大可能会在10nm工艺使用QWFEN量子井场效电晶体工艺,同时还会使用新型的半导体材料,N型使用铟镓砷(In0.53Ga0.47As),P型使用应变锗(strained germanium)

按照他的分析,Intel最早会在2016年的10nm工艺上使用这些外星科技,将电晶体运行电压从0.7V降低到0.5V,而三星、TSMC、Globalfoundries等公司要等到7nm工艺才有可能使用这些新技术,依然要比Intel落后一代。

评论