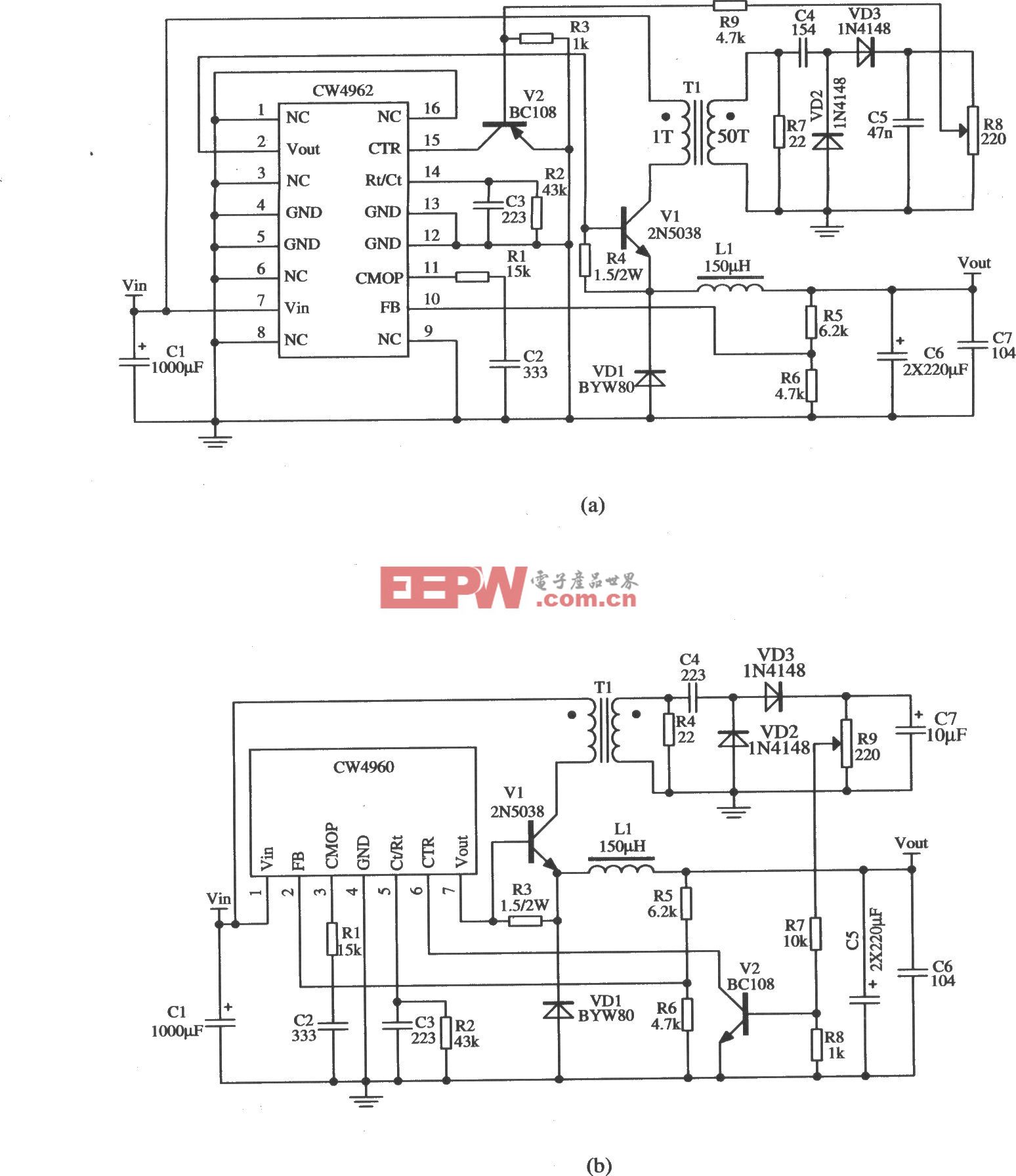

用于准谐振反激式变换器的新型数字系统解决方案(08-100)

简介

本文引用地址://m.amcfsurvey.com/article/92121.htm与模拟电源管理IC相比,数字IC可以实现设计更灵活、集成度更高且允许更大生产公差的系统解决方案。本文将介绍可提高系统性能的用于准谐振反激式控制器的数字电路。

在能源问题受到越来越广泛关注的今天,大部分电源标准不仅规定了满载时的效率,而且还规定了整个负载范围内的平均效率。例如,能源之星2.0(Energy Star 2.0)规定的平均效率为87%。数字降频方法可以更方便地提高平均效率。另外,数字电路可以更精确地模拟非线性的最大输入功率极限曲线。英飞凌新型ICE2QS02G控制器将这些数字特性与其他必要功能融合在一起,为客户提供卓越的系统解决方案。

ICE2QS02G的数字特性

数字降频带来负载降低

由于其开关损耗比固定频率的反激式变换器低且EMI性能更好,准谐振反激式变换器得到了广泛的应用。准谐振反激式变换器面临的挑战之一是其开关频率随输出功率的下降而上升。这抵消了通过准谐振方式工作而带来的效率提升,特别是在中等负载或低负载条件下。为了解决这一问题,英飞凌的准谐振PWM控制器ICICE2QS02G采用了数字降频策略。

ICE2QS02G同时采用数字信号处理电路和模拟信号处理电路。数字信号处理电路包括一个加/减计数器、一个过零信号计数器(ZC-计数器)和一个数字比较器;模拟电路包括一个电流测量单元和一个比较器。导通和关断的时间点分别由数字电路和模拟电路决定。

加/减计数器储存变压器退磁后主电源开关接通之前应忽略的过零信号数,该存储数由反馈电压VFB确定。VFB中包含了输出功率的信息。因此,加/减计数器中的存储数随VFB的数值而改变,以实现根据输出功率的变化来调整功率MOSFET的关断时间。

加/减计数器存储数的变化与反馈电压之间的关系如表1所示。在每个48 毫秒的时钟周期内,内部电路将反馈电压VFB分别与VRL、VRH和VRM这三个阀值电压进行比较,根据比较结果,加/减计数器的存储数相应增加、保持不变或减少。对于ICE2QS02G,过零信号的数量被限制在7个以内,因此加/减计数器的存储数也在1和7之间变动,而对于任何超出这一范围的计数则不予理会。当VFB超过VRM电压时,加/减计数器的存储数被初始化为1,以使系统能对负载的突然增加迅速做出反应。在启动时,加/减计数器也被初始化为1,以确保满载启动时的效率最高。

表 1 加/减计数器的操作

ZC计数器存储MOSFET被关断后的过零信号数。VZC的降压斜坡每与100毫伏的阀值交叉一次,一个过零信号就被检测到,ZC计数器的存储数相应增加1。一旦ZC计数器的存储数与加/减计数器的存储数相等,MOSFET就导通。

评论