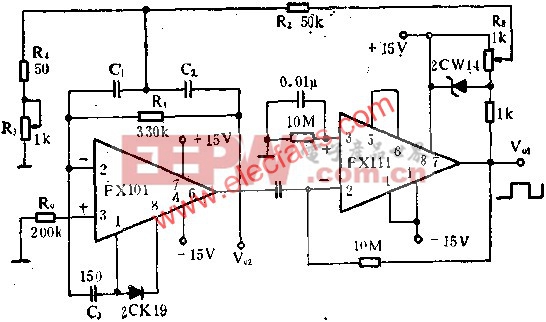

- 图中所示是用运算放大器组成的阶梯波发生器线路.阶梯波发生器产生的阶梯信号,在无线电遥测,调频信号磁带记录以及数字电压表中较为有用,有时作为比较基准电压.产生阶梯波的方法也较多,图示线路是一个较实用的线路,图中

- 关键字:发生器电路图阶梯组成放大器运算

- 图中所示是用高性能运放FX101和精密电压比较器FX111组成的正弦波和矩形波发生器线路.图示线路只要改变R3,就可以在很宽的范围内改变振荡频率.FX111输出(V01)为矩形波,通过FX101带通滤波,FX101输出(V02)为正弦波,R3(1K

- 关键字:电路图发生器矩形

- 本设计的超声波发生器是利用单片机生成初始信号,然后经过一系列处理电路的作用后生成用来杀灭水蚤的超声波,成本低、效果好,可以在农业上加以采用。在此对3个模块进行设计: (1)信号发生模块。12 MHz的8051单片

- 关键字:设计方案发生器超声波单片机基于

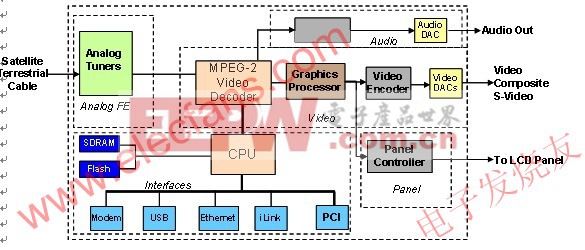

- 随着集成技术的不断发展,基于锁相环(PLL)的硅芯片时序解决方案的应用越来越普遍,为那些需要多种频率的设计方案提供了更洁净、更稳定的时钟选择方案。本文的目的在于详细论述采用硅芯片时序解决方案来解决时序设计

- 关键字:设备设计应用娱乐数字扩频时钟相环

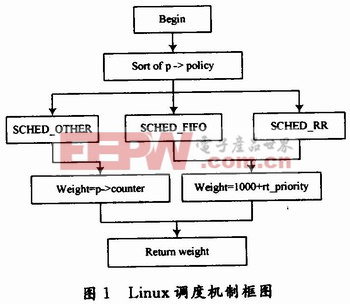

- 基于APIC时钟的嵌入式Linux内核实时化研究,在分析目前Linux的各种实时化方法的基础上,提出了基于APIC时钟修改的方法,以获得更高的硬实时性能。对APIC中断函数进行修改,将APIC中断和8254中断排序,使得硬实时中断的优先级大于普通8254中断,从而获得了更高的实时性能。多组仿真实验验证了该方法的有效性。

- 关键字:内核实时研究Linux嵌入式APIC时钟基于

- 凌力尔特公司 (Linear Technology Corporation) 推出硅振荡器 LTC6992,该器件是 TimerBloxTM 硅定时器件系列的最新成员。LTC6992 针对 3.81Hz 至 1MHz 的输出频率提供简单和准确的脉冲宽度调制 (PWM) 功能。该器件的频率可用 1 至 3 个电阻器设定,具有保证低于 1.7% 的频率误差。此外,频率可以通过单独的控制电压来动态地控制。输出脉冲宽度 (占空比) 简单地用一个 0V 至 1V 的模拟信号控制。LTC6992 在加电后 500

- 关键字:凌力尔特时钟LTC6992

- FPGA全局时钟资源相关原语及使用, FPGA全局时钟资源一般使用全铜层工艺实现,并设计了专用时钟缓冲与驱动结构,从而使全局时钟到达芯片内部的所有可配置单元(CLB)、I/O单元(IOB)和选择性块RAM(Block Select RAM)的时延和抖动都为最小。为了适应复杂

- 关键字:相关使用资源时钟全局FPGA

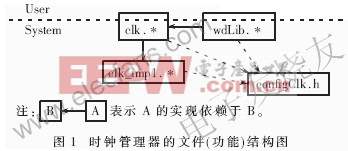

- 嵌入式时钟管理器的设计与实现, 目前,在嵌入式产品的研发中,低档微处理器软件多采用裸机开发模式实现。在这种开发模式中,常有如下需求: (1) 在经历特定的时间段后,执行特定操作; (2) 根据给定周期执行特定操作。 传统的作法是利用

- 关键字:实现设计管理时钟嵌入式

- 电子产品世界,为电子工程师提供全面的电子产品信息和行业解决方案,是电子工程师的技术中心和交流中心,是电子产品的市场中心,EEPW 20年的品牌历史,是电子工程师的网络家园

- 关键字:DSP设计电源时钟干扰布局

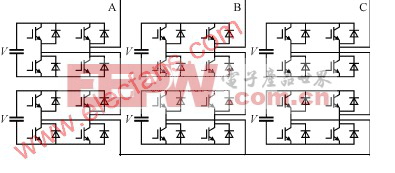

- 基于DSP与CPLD的三相五电平变频器PWM脉冲发生器, 1 引言 近年来,多电平变换器成为电力电子研究的热点之一,它主要面向中压大功率的应用场合。目前,有三种基本的多电平变换器拓扑结构[1]:①二极管箝位型;②飞跨电容型;③级联型。 几种拓扑结构各有其优缺点

- 关键字:PWM脉冲发生器变频器电平DSPCPLD三相五基于

- 如何利用GPS OEM来进行二次开发,产生高精度时钟发生器是一个研究的热点问题。在电力系统、CDMA2000、DVB、DMB等系统中,高精度的GPS时钟发生器(GPS同步时钟)对维持系统正常运转有至关重要的意义。如在DVB-T单频网(S

- 关键字:方案技术发生器时钟GPS

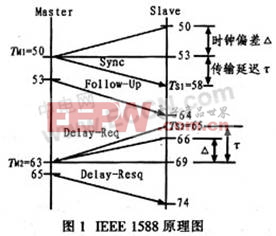

- 为实现分布式系统高精度同步数据采集及实时控制,提出一种基于IEEE 1588协议的分布式系统时钟同步方法。通过分析影响同步精度的因素,采用FPGA设计时间戳生成器,并且采用晶振频率补偿时钟解决时间戳的精确获取和从时钟相对主时钟的频率纠偏等问题。

- 关键字:分布式系统应用技术同步IEEE时钟基于收发器

- 高性能模拟与混合信号IC领导厂商Silicon Laboratories (芯科实验室有限公司)今日发表在线时钟树设计服务,客户可利用此服务迅速获得Silicon Labs经验丰富的应用工程团队提供的定制化时钟架构建议,进一步简化设计、降低BOM材料成本,将开发风险降至最低。此外,Silicon Labs可提供业界最短的元器件交货期(约两星期或更短时间),从而大幅加速客户产品的上市时间。 在强调性能的应用中,通常采用振荡器、时钟发生器和频率缓冲器的组合,为高速SerDes元器件、FPGA、处理器

- 关键字:芯科实验室时钟

- 针对X光安检机系统控制信号传输中采用传统串行通信方式所存在的问题,提出一种利用数字锁相环技术实现串行数据时钟提取的硬件解决方案。该设计基于FPGA进行开发,并针对安检机中串行控制数据传输的数字锁相环进行研究,设计了适用于FPGA的串行时钟提取系统,最终采用Verilog语言实现。该设计经过安检机系统的硬件平台实际测试,最终经过Signal TapⅡ读取实时数据进行验证,可以论证该方案的时钟捕捉周期短,捕捉精度也满足安检机系统要求,从而实现了安检机系统数字控制信号的单线路传输,有效地提高传输的可靠性。

- 关键字:设计实现提取时钟控制信号安检时钟提取

- 针对逆变控制领域的需求,采用自然采样法设计一个基于SOPC的SPWM脉冲发生器。在系统中,结合DDS数字频率合成技术产生正弦调制波。使用Vet4log语言编程实现可逆计数器,利用可逆计数器形成一个完整的三角波。然后将同一时刻的正弦函数值与三角函数值相比较,形成一路脉冲调制波。最后为防止同相桥臂功率器件的同时导通,经过死区延时部分,形成最终的SPWM脉宽调制波。基于SOPC系统的SPWM脉冲发生器既简化电路设计,又提高系统的可靠性、精确性,并通过实验验证实该系统设计的有效性、稳定性。

- 关键字:发生器实现脉冲SPWMSOPC基于编解码器

时钟(clk)发生器介绍

您好,目前还没有人创建词条时钟(clk)发生器!

欢迎您创建该词条,阐述对时钟(clk)发生器的理解,并与今后在此搜索时钟(clk)发生器的朋友们分享。

创建词条

关于我们-

广告服务-

企业会员服务-

网站地图-

联系我们-

征稿-

友情链接-

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473