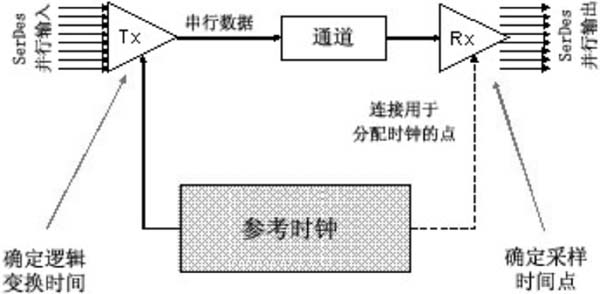

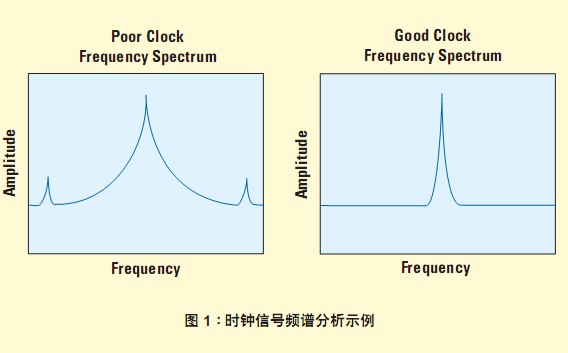

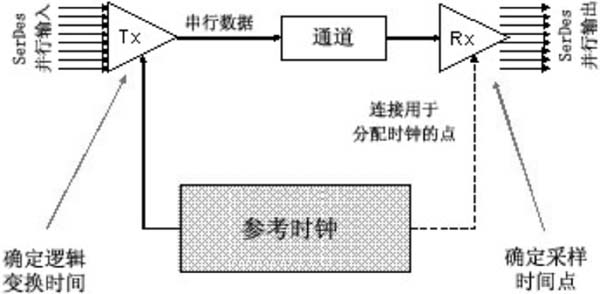

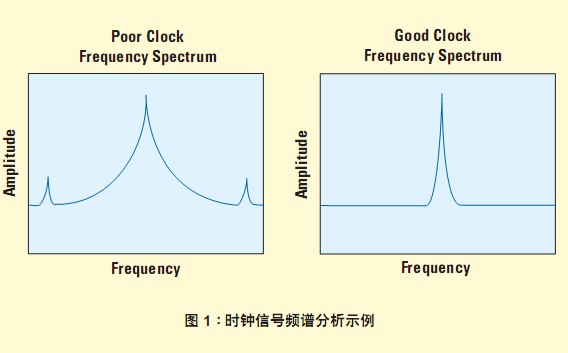

- 随着数据速率的提高,时钟抖动分析的需求也在与日俱增。在高速串行数据链路中,时钟抖动会影响发射机、传输线和接收机的数据抖动。保证时钟质量的测量也在不断发展。目前的重点是针对比特误码率,在时钟性能和系统性能之间建立直接联系。我们将探讨参考时钟的作用和时钟抖动对数据抖动的影响,并讨论在E5052B信号源分析仪(SSA)上运行的Agilent E5001A精确时钟抖动分析应用软件所配备的全新测量技术。该应用软件提供了前所未有的强大能力,可以对随机抖动(RJ)和周期抖动(PJ)分量超低RJ测量和实时抖动频谱分析

- 关键字:时钟抖动PLL响应

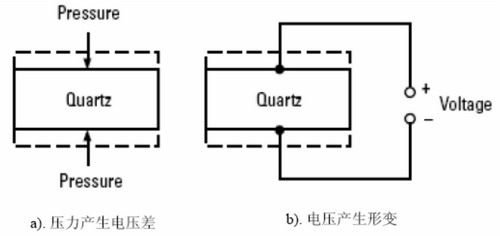

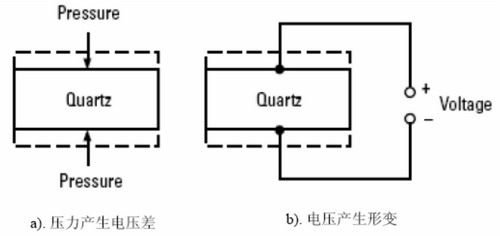

- 在通讯手持设备当中,参考时钟的贡献就像心脏对人体的作用一样,丝毫的差异都将导致系统功能的紊乱。之所以定义它为参考,是因为这类产品能否正常工作完全依赖于该时钟的精确度;而且一旦有误差存在,该误差就会随着倍频的增加而介入应用端的工作频段,无论是基带的数字和模拟部分还是射频的上变频和下变频都会受到影响。通常参考时钟所采用的中心频点都在10MHz~30MHz,而且目前大多数都采用13MHz,20MHz,或26MHz,尤其是当射频和基带共用参考时钟时以13MHz和26MHz最多。

- 关键字:通讯时钟石英晶体

- 随着模/数转换器的数据转换取样率提高至每秒千兆个取样 (GSPS) 以上的水平,数据转换系统必须作出相应的配合,才可支持这样高的转换率,而其他支持性的模拟元件也必须产生系统所需的高频信号,然后将之放大。系统设计工程师除了要对模拟信号路径有深入的了解之外,也要彻底认识取样时钟以及系统如何以高位速率捕捉数字信号。本文 将会就有关上述两个重要的问题提供多个不同的解决方案。以下所讨论的资料有助深入了解采用高性能模/数转换器的系统。

- 关键字:美国国家半导体时钟数据捕捉

- 由于各种人群的皮肤阻抗的动态范围不一样,甚至同个人在不同的时间、不同的环境下皮肤阻抗的动态范围也不一样。因此,在皮肤阻抗检测系统中,刺激器需要根据不同的人群以及不同的环境,产生不同频率、不同脉宽的刺激信号,才能保证检测系统可以测量到人体皮肤的真实阻抗。

MCS-51单片机系统有3个定时器可以产生方波,而且方波的脉冲频率及宽度可以由软件设定,这种产生脉冲的方式具有很大的灵活性。上位机软件LabVIEW同下位机通信时,将下位机所要产生的脉冲的参数通过串口传给下位机,以便实现利用LabVI

- 关键字:发生器脉冲单片机LabVIEW基于脉冲发生器

- Megal6是一款采用先进RISC精简指令,内置A/D的8位单片机,可支持低电压联机Flash和EEPROM写入功能:同时还史持Basic和C等高级语言编程。用它设计电子时钟不仅成本低,硬件简单,而且很容易实现系统移植。介绍了如何利用AVR系列单片机Megal6及1602字符液晶来设计电子时钟的方法,同时给出了相应的电路原理及部分语言程序。

- 关键字:电子AVR单片机Megal6时钟设计基于字符液晶

- 介绍了一种采用FPGA设计的SDH设备时钟的构成及设计原理;并给出了相关的测试结果;测试结果表明该SDH设备时钟完全满足ITU-T G.813建议规范的各项时钟指标要求。

- 关键字:FPGASDH设备时钟

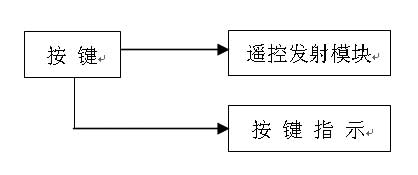

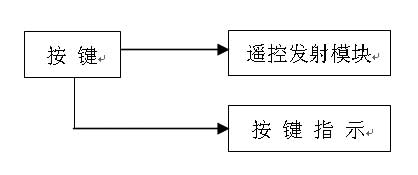

- 引言 LED时钟显示屏的长时间使用,会产生一定的累加误差,故使用一段时间需进行校正,但大屏幕时钟显示器,通常悬挂在较高处,时间的调整与修改需工作人员爬到高处进行操作,既不方便,又不安全,如何完善电路结构,设计出安全、实用的遥控电路是很多电子爱好者一直关注的问题。本系统设计了一种采用无线遥控修改时钟数据的LED时钟显示屏。 系统组成 1 遥控发射器 图1遥控发射器框图 遥控发射器由6个按键、F06A无线发射芯片、4个隔离二极管等元件组成。如图1所示。 2 LED时

- 关键字:LED时钟显示屏单片机遥控

- SDH、同步以太网设备时钟的高效率实现方法,本文介绍几种类型的SDH、同步以太网等同步设备时钟的器件设计方案,比较它们在易用性、综合成本等方面的差异。指出采用模块化的设计理念是高效率地完成包括设计和生产两个方面内容的产品实现之最佳途径。这是专业化分工的必然趋势,同时也符合通信设备制造商希望提高产品质量、降低产品成本、加快上市时间的要求。

- 关键字:高效率实现方法时钟设备同步以太网SDH

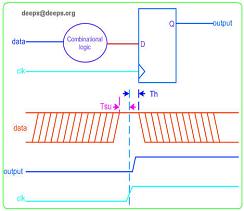

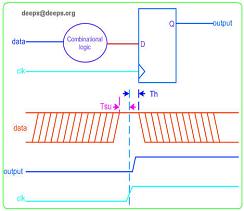

- 时钟是整个电路最重要、最特殊的信号,系统内大部分器件的动作都是在时钟的跳变沿上进行, 这就要求时钟信号时延差要非常小, 否则就可能造成时序逻辑状态出错;因而明确FPGA设计中决定系统时钟的因素,尽量较小时钟的延时对保证设计的稳定性有非常重要的意义。 1.1 建立时间与保持时间 建立时间(Tsu:set up time)是指在时钟沿到来之前数据从不稳定到稳定所需的时间,如果建立的时间不满足要求那么数据将不能在这个时钟上升沿被稳定的打入触发器;保持时间(Th:hold time)是指数据稳定后

- 关键字:FPGA时钟

- JTAG技术简介收缩技术(shrinkingtechnology)的一个劣势在于,测试小型器件的复杂程度急剧升高。当...

- 关键字:时钟速率控制密度仿真扫描

- 致力于丰富数字媒体体验、提供领先的混合信号半导体解决方案供应商 IDT® 公司(Integrated Device Technology, Inc.; NASDAQ: IDTI)今天宣布,推出专门用于超便携 PC(ultra-mobile PC,UMPC)的超低功耗时钟器件系列。这些超低功耗时钟器件最低只需 1.5 伏电压,而标准的时钟器件需要 3.3 伏,这将延长 UMPC 的电池寿命。 这些 IDT UMPC 时钟器件还可以帮助拓展 UMPC 的无线信号范围并提高带宽,从而促成更快的

- 关键字:IDT低功耗时钟

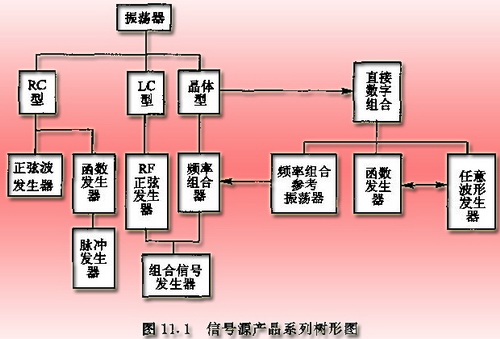

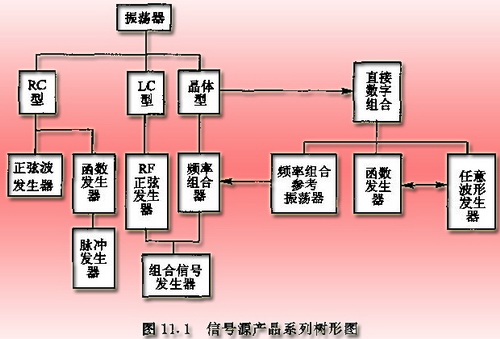

- 使用一个激发装置(即信号源)来激励一个系统,以便观察、分析它对激励信号的反映如何,这是电子测试技术的标准实验之一。在设计、制造飞机时,需要事先了解机体及其有关设备在各种气流、雷击、雨水、温变干扰下的反映情况;在发展冶炼技术时,需要了解炉内物态随炉脸温度燃油器喷口温度而变化的动态过程;在分析一个电子线路时,常常需要了解输出信号频率及振幅与输入信号频率及振幅之间的关系。这样,在进行上述过程的硬件或软件的模拟实验时.就需要人为地产生各种模仿的信号。系统在这些模仿的信号的激励下产生各种反应,因此,称它们为激励

- 关键字:转换器存储器函数信号发生器激发装置信号源

时钟(clk)发生器介绍

您好,目前还没有人创建词条时钟(clk)发生器!

欢迎您创建该词条,阐述对时钟(clk)发生器的理解,并与今后在此搜索时钟(clk)发生器的朋友们分享。

创建词条

关于我们-

广告服务-

企业会员服务-

网站地图-

联系我们-

征稿-

友情链接-

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473