针对未来十年 “All Programmable”器件的颠覆之作

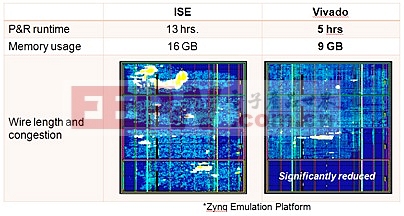

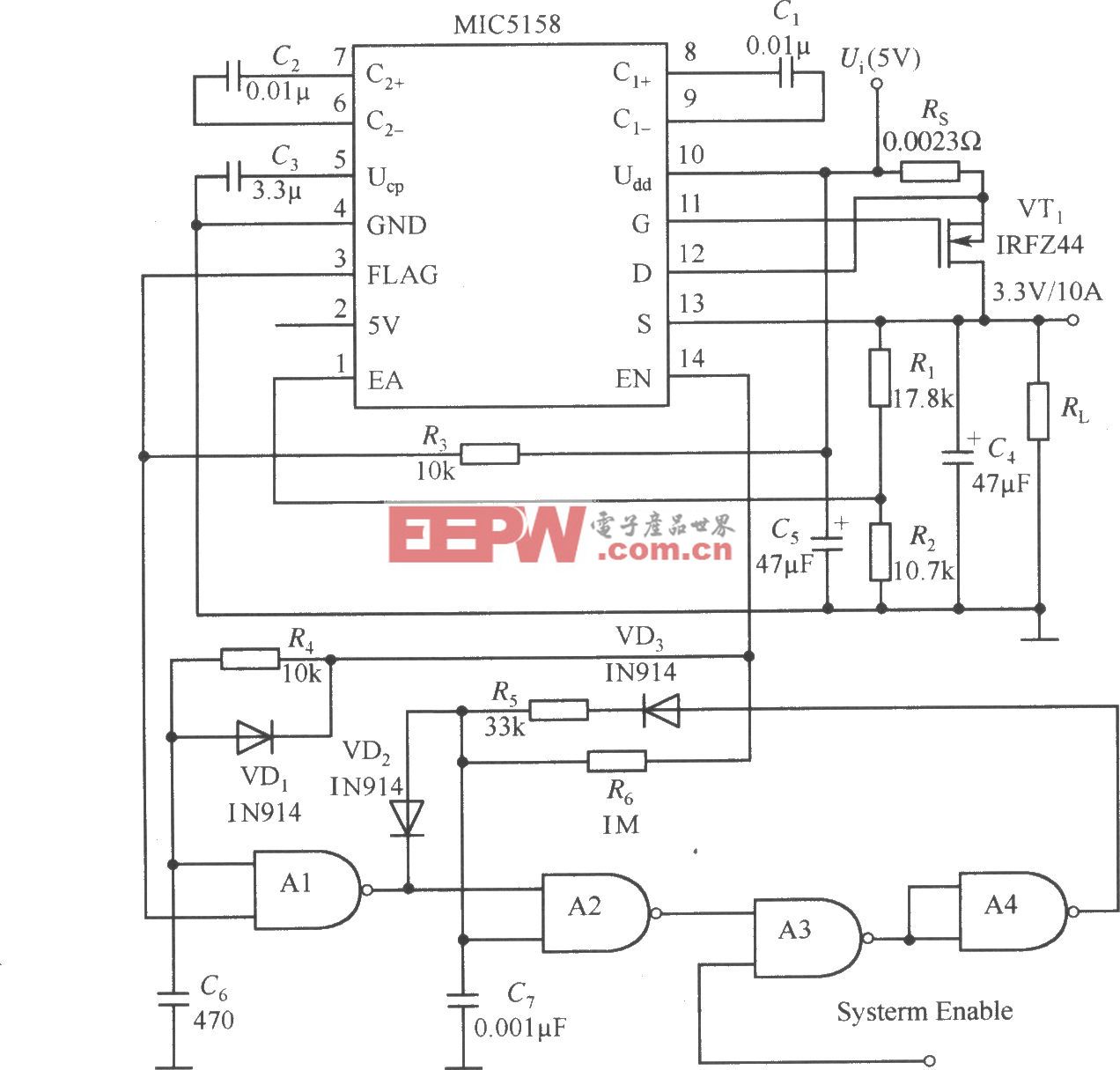

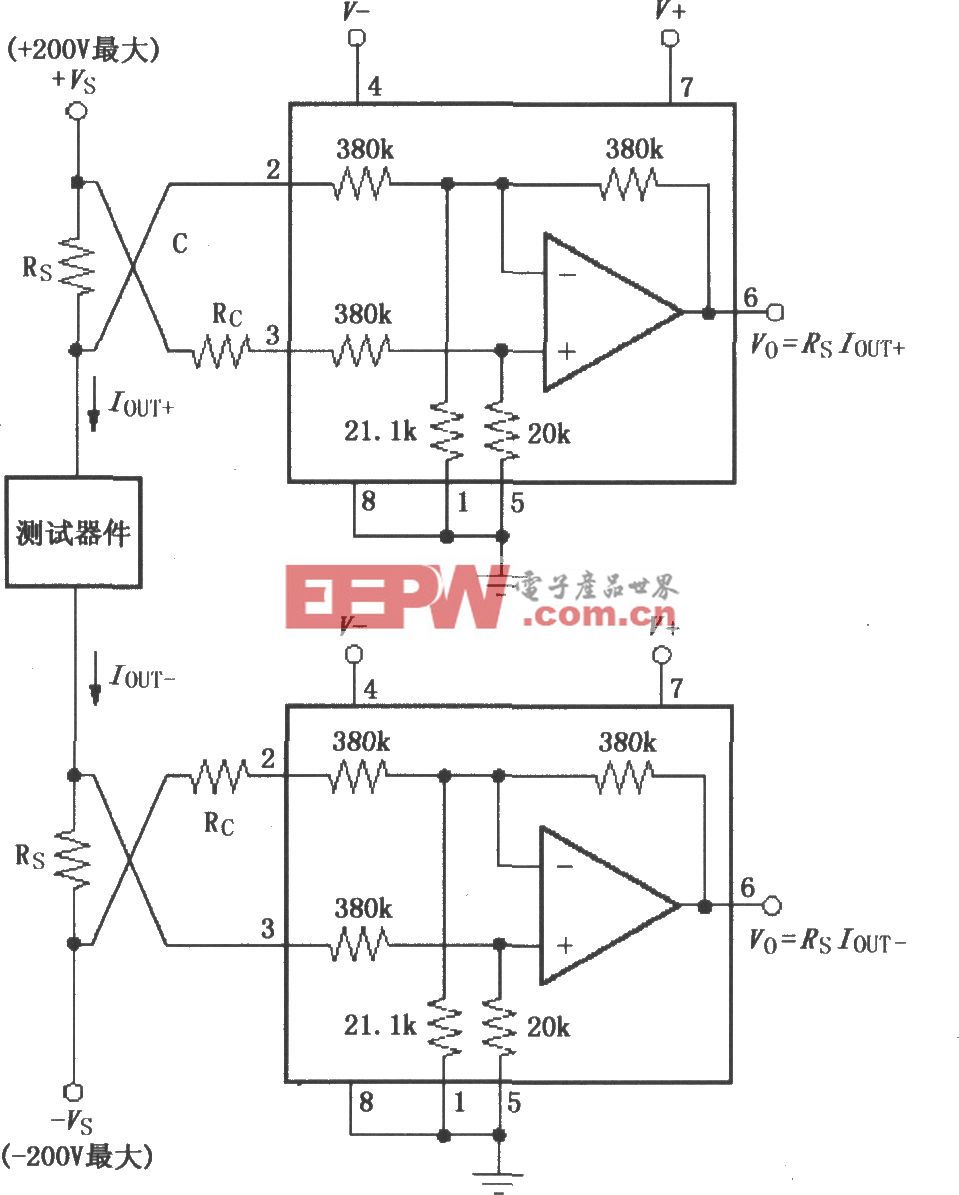

为展现这种优势,赛灵思在 ISE设计套件和 Vivado 设计套件中用按键式流程方式同时运行针对赛灵思 Zynq-7000 EPP 仿真平台开发的原始 RTL,同时将每种工具指向赛灵思世界最大容量的 FPGA 器件——采用堆叠硅片互联技术的 Virtex-7 2000T FPGA。这样 Vivado 设计套件的布局布线引擎仅耗时 5 个小时就完成了 120 万逻辑单元的布局,而 ISE 设计套件则耗时长达 13 个小时(图 2)。而且采用 Vivado 设计套件实现的设计拥塞明显降低(设计中显示为灰色和黄色的部分),器件占用面积较小,这说明总体走线长度缩短。Vivado 设计套件实现方案还体现出更出色的内存编译效率,仅用9GB就实现设计要求的内存,而 ISE 设计套件则用了 16GB。

本文引用地址://m.amcfsurvey.com/article/131872.htmFeist 表示:“从本质上来说, 你看到的就是 Vivado 设计套件在满足所有约束条件下,实现整个设计只需占用 3/4 的器件资源。这意味着用户可以为自己的设计添加更多的逻辑功能和片上存储器,甚至可以采用更小型的器件。”

图 2:Vivado 设计套件的多维分析算法可创建专门针对最佳时序、拥塞和走线长度(而不仅仅只是针对最佳时序)优化的布局。

功耗优化和分析

当今时代, 功耗是FPGA设计中最关键的环节之一。因此,Vivado设计套件的重点就是专注于利用先进的功耗优化技术,为用户的设计提供更大的功耗降低优势。“我们在技术上采用了目前在ASIC工具套件中可以见到的先进的时钟门控制技术,通过该技术可以拥有设计逻辑分析的功能,同时消除不必要的翻转”Feist表示 “具体来说,新的技术侧重于翻转因子 ‘alpha’,它能够降低30%的动态功耗”Feist说,赛灵思去年在ISE设计套件中开始应用该技术, 并一直沿用至今。 Vivado将继续加强这一技术的应用。

此外,有了这一新的可扩展的数据共享模型,用户可以在设计流程的每一个阶段得到功耗的估值,从而可以在问题发展的前期就能预先进行分析, 从而能够在设计流程中,先行解决问题。

简化工程变更单(ECO)

增量流量让快速处理小的设计更改成为可能,每次更改后只需重新实现设计的一小部分,使迭代速度更快。它们还能在每个增量变化之后实现性能的表现,从而无需多个设计迭代。为此,Vivado设计套件还包括对一个流行的ISE FPGA编辑器工具的新的扩展,称为Vivado器件编辑器。Feist说,在一个布局布线设计上使用Vivado器件编辑器,设计师现在有能力去做移动单元, 重新布线, 连接一个寄存器输出作为调试管脚, 修改DCM或者查找表(LUT)的参数的工程变更单(ECO)——在设计周期的后期,无需通过返回设计重新综合和实现。他说,目前行业没有任何其他FPGA设计环境可以提供这种级别的灵活性。

基于业界标准而打造

四年半前, 当赛灵思开始从头打造Vivado设计套件的时候,架构打造的首要任务,就是用标准的设计环境代替专有格式。致力于打造一个开放的环境,让客户能够用 EDA 工具和第三方 IP 进行扩展。例如,Vivado 设计套件可支持 SDC(Synopsys 设计约束)、ARM AMBA AXI 4 IP互联标准、IP-XACT IP封装和交付标准,并且在新环境中提供了强大的互动 TCL 脚本功能。。

评论