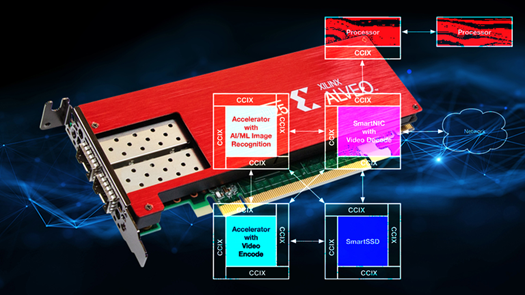

针对未来十年 “All Programmable”器件的颠覆之作

流程自动化,非流程强制化

本文引用地址://m.amcfsurvey.com/article/131872.htm在Vivado设计套件构建过程中,赛灵思工具团队遵循这样的原则“自动化设计方式,不强制设计方式”。Feist 说:“不管用户用 C、C++、SystemC、VHDL、Verilog、System Verilog、MATLAB 还是 Simulink 开始编程,也不管他们用的是我们的 IP 还是第三方的 IP,我们提供了一种实现所有流程自动化,帮助客户提高生产力的方法。我们还充分考虑到我们的用户的各种技能水平和偏好,既能满足需要全按键式流程的客户的要求,也能满足在设计流程的每一步都进行分析的客户的要求,甚至还能满足那些认为用 GUI 的是低手,喜欢用 TCL 以命令行或批处理模式完成全部设计流程的客户的要求。用户能够根据自己的特定需求,选用套件功能。”

为进一步增强所有用户的设计体验,赛灵思在Vivado设计套件中加入了某些奇妙的新功能,同时为深受客户赞誉的 FPGA 编辑器增加了芯片编辑器功能。

IP 封装器、集成器和目录

赛灵思的工具架构团队把重点放在新套件专门的 IP 功能设计上,以便于 IP 的开发、集成与存档。为此,赛灵思开发出了 IP 封装器、IP 集成器和可扩展 IP 目录三种全新的 IP 功能。

Feist 表示:“今天很难找到不采用IP 的 IC 设计。我们采用业界标准,提供专门便于 IP 开发、集成和存档/维护的工具,这都有助于我们生态系统合作伙伴中的 IP 厂商和客户快速构建 IP,提高设计生产力。目前已有 20 多家厂商提供支持该最新套件的 IP。”

采用 IP 封装器,赛灵思的客户、赛灵思公司自己的 IP 开发人员和赛灵思生态环境合作伙伴可以在设计流程的任何阶段将自己的部分设计或整个设计转换为可重用的内核,这里的设计可以是 RTL、网表、布局后的网表甚至是布局布线后的网表。IP 封装器可以创建 IP 的 IP-XACT 描述,这样用户使用新型 IP 集成器就能方便地将 IP 集成到未来设计中。IP 封装器在 XML 文件中设定了每个 IP 的数据。Feist 说一旦 IP 封装完成,用 IP 集成器功能就可以将 IP 集成到设计的其余部分。

Feist 说:“IP 集成器可以让客户在互联层面而非引脚层面将 IP 集成到自己的设计中。可以将 IP 逐个拖放到自己的设计图(canvas)上,IP 集成器会自动提前检查对应的接口是否兼容。如果兼容,就可以在内核间划一条线,然后集成器会自动编写连接所有引脚的具体 RTL。”

Feist 表示:“这里的重点是可以取出已用 IP 集成器集成的四五个模块的输出,然后通过封装器再封装。这样就成了一个其他人可以重新使用的 IP。这种 IP 不一定必须是 RTL,可以是布局后的网表,甚至可以是布局布线后的网表模块。这样可以进一步节省集成和验证时间。”

第三大功能是可扩展 IP 目录,它使用户能够用他们自己创建的 IP 以及赛灵思和第三方厂商许可的 IP 创建自己的标准 IP 库。赛灵思按照 IP-XACT 标准要求创建的该目录能够让设计团队乃至企业更好的组织自己的 IP,供整个机构共享使用。Feist 称赛灵思系统生成器 (System Generator) 和 IP 集成器均已与Vivado可扩展 IP 目录集成,故用户可以轻松访问编目 IP 并将其集成到自己的设计项目中。

Vivado 产品营销总监 Ramine Roane指出:“以前第三方 IP 厂商用 Zip 文件交付的IP格式各异,而现在他们交付的 IP,不仅格式统一,可立即使用,而且还与 Vivado 套件兼容。”

Vivado HLS 把 ELS带入 主流

可能 Vivado 设计套件采用的众多新技术中,最具有前瞻性的要数新的 Vivado HLS(高层次综合)技术,这是赛灵思 2010 年收购 AutoESL 后获得的。在收购这项业界最佳技术之前,赛灵思对商用 ESL 解决方案进行了广泛评估。市场调研公司 BDTI 的研究结果帮助赛灵思做出了收购决策。

Feist 表示:“Vivado HLS 全面覆盖 C、C++、SystemC,能够进行浮点运算和任意精度浮点运算。这意味着只要用户愿意,可以在算法开发环境而不是典型的硬件开发环境中使用该工具。这样做的优点在于在这个层面开发的算法的验证速度比在 RTL 级有数量级的提高。这就是说,既可以让算法提速,又可以探索算法的可行性,并且能够在架构级实现吞吐量、时延和功耗的权衡取舍。”

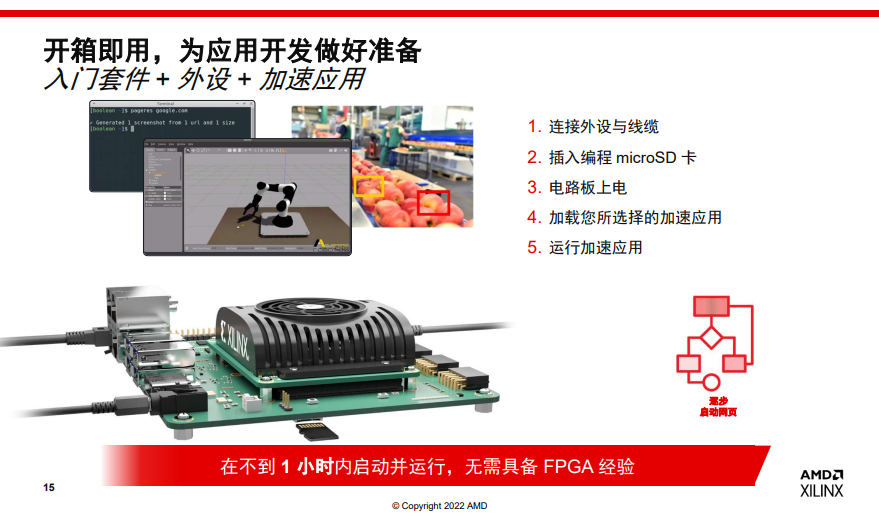

设计人员使用 Vivado HLS 工具可以通过各种方式执行各种功能。为了演示方便,Feist 讲解了用户如何通过一个通用的流程进行 Vivado HLS 开发 IP 并将其集成到自己的设计当中。

评论