c制程渐成熟 有助3C产品微缩设计

行动运算产品市场持续朝产品薄化方向设计,目前相关设计多使用整合晶片减少元件用量,对于异质核心的封装整合,若仍使用旧有的封装技术将会造成成品元件仍具一定程度占位面积,必须利用堆叠与更复杂的3DIC技术进行元件整合的积极微缩设计…

本文引用地址://m.amcfsurvey.com/article/167314.htm矽晶片的制程技术,一直是推进行动终端产品跃进式升级、改善的关键驱动力,以往透过SoC(systemonachip)将不同用途的异质核心进行整合,目前已经产生简化料件、缩减关键元件占位面积的目的,但随着使用者对于行动装置或可携式装置的薄化、小型化要求越来越高,异质功能晶片除要求高度整合成单晶片外,也对整合的元件体积要求越来越高!还必须在整合元件的占位面积进一步进行缩减。

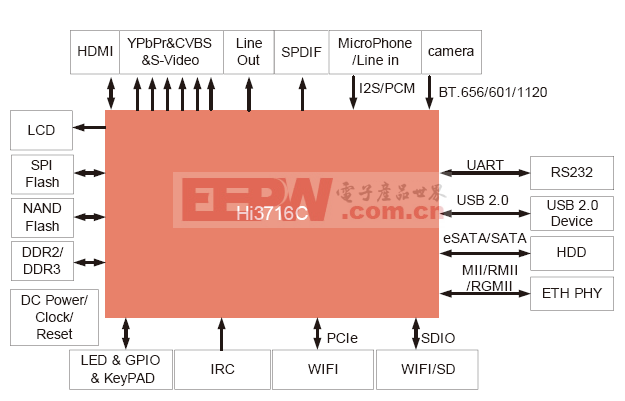

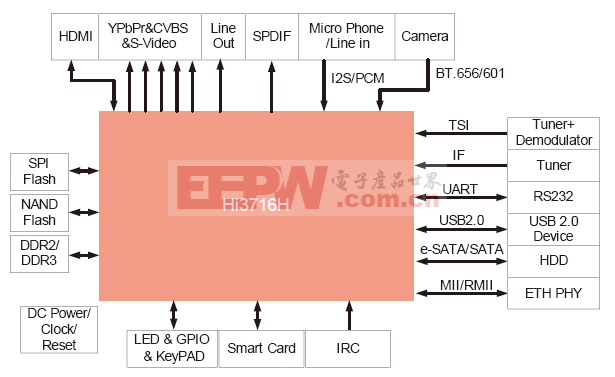

SoC整合的趋势与效益明显,越来越多晶片产品采用高度整合方式简化系统架构复杂度。Altera

记忆体晶片构造较单纯,使用3DIC制程具大幅扩增容量效益,图为IBM利用3DIC技术制作的多记忆体晶片堆叠封装构造示意图。IBM

WireBonding使用效益有限业者积极发展微缩制法

早期的整合封装方式,是将各功能晶片利用打线连接(WireBonding),虽可在功能性满足多晶片整合的要求,同时也可以缩减至少30%~40%的载板占位面积,因为功能晶片间的传输汇流排、电子线路等已经在同一个封装内处理完成,对于晶片对外的线路布线需求即消失了,自然载板即可再进一步缩减。

但在得到30%~40%载板面积缩减的跳跃式巨幅改善后,想进一步进行缩减,在制程与IC技术却碰到新的开发瓶颈,因为在物理限制下晶片的微缩程度已经达到高峰,若要进一步再微缩设计获得较大幅的改善效益,反而要从封装制程上着手。例如,原本平整利用金属打线整合的多晶片封装,改用晶片堆叠方式进行,甚至连较占空间的金属打线都改用IC制程处理,进一步缩减晶片间在封装体内部的间隙,达到更大幅度的晶片微缩设计。

TSV技术可有效提升IC功能

即便透过IC制程的封装改善,仅能再把晶片本身体积进行有限的微幅缩减,虽对于异质核心的整合晶片本身微缩效益有限,若将此技术整合于记忆体之类的同质晶片封装,由于利用IC制程的整合设计可让同时可装载的晶片数量增加,让原先受限于封装技术无法大量堆叠的晶片进一步进行微缩整合,即可创造倍数计的应用价值提升。

而在众多微缩制程的封装技术中,以TSV(Through-SiliconVia)直通矽晶穿孔封装技术目前颇受业界关注,TSV为能让3DIC封装满足IC业界摩尔定律(Moore’sLaw)产品演进速度的一种晶片内的互连技术。TSV设计概念是源自高密度多层印刷电路板(PCB)设计,TSV封装方式可以如同千层派般层层堆叠数片功能晶片,封装技术将电力互相连接的三次元(3D)堆叠封装(StackPackage)方式,这可以使TSV封装方法较传统采平面(2D)形式配置晶片的封装技术进入3D的晶片堆叠技术,目前TSV技术已有相关产品应用于市场。

TSV难度高线路成形制法为成功关键

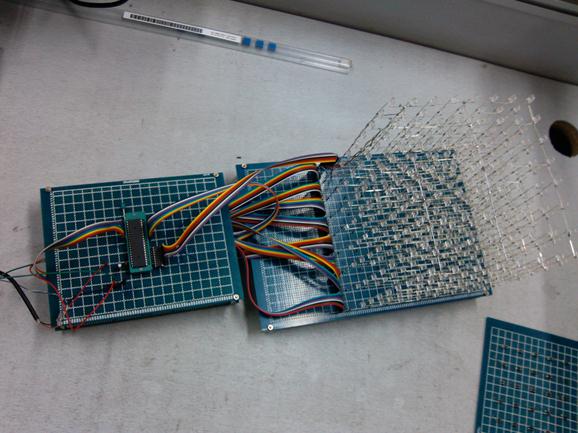

以TSV立体堆叠技术来说,实践TSV封装方案的关键包括晶圆薄化、钻孔、导电材质填孔、晶圆与晶圆间的连接处理等,TSV的晶片堆叠方式并不是采行以往2DIC整合常见的打线接合(WireBonding)方式来制作不同晶片的连接处理,而是使用在晶片上进行钻孔打洞方式于晶片底部填入金属材料。

实际的作法与步骤是:在每一组矽晶圆以蚀刻或雷射型式来进行钻孔(via)处理,制作出可以贯通每一层晶片的导线空间(此为前置处理步骤),接着再利用铜、多晶矽、钨…等导电材料来填满各层晶片预先处理的线路管径,透过导孔以导电物连结后形成电子电路通道(内部接合线路),进行讯号或电力连接目的,当内部线路处理完成后,再将晶圆或者是晶粒施加薄化研磨处理,或再搭配堆叠、结合(Bonding)等加工制程进行制作,TSV即为将多IC晶片整合的关键堆叠技术。

TSV技术其实也不见得仅能将导线设置于晶片的四周。因为TSV的观念是全3D立体布线的思维,原有2D概念的原件布局可以改垂直方向的3D堆叠,至于内部连接线路除了利用晶片周围进行连接外,TSV技术也可将线路连接处设计于穿越晶片本身,连接线也可以在晶片中间或是设置需求处。这种弹性的线路连接方式,可以进一步简化内部线路连接型态,可让晶片内的传输线距以最佳化的距离进行设计,使内部连接路径以更短的距离达到连接需求。

采行TSV制法效益多已有记忆体产品导入市场

TSV除改善传输或信号线距外,因为点对点的传输线距使得导通路径缩短,这在电子电路应用中可以产生相当多的效益!例如,该线路可以传输更高频的信号,该线路的阻抗也可以因传输距离缩减而相对应减少,自然线路杂讯问题也可获得改善,元件的效能同时可以获得提升,对于部分高效应用可能产生的晶片核心高热现象,也可善用TSV的线路设置弹性,将容易聚集高热的关键元件核心进行导电线路制作,除讯号传递效果外也可将晶片核心的高热透过多元导通线路进行内部温度逸散途径。

另外,TSV技术可以让异质晶片堆叠透过连接线达到高密度构装,并可应用于类比、数位或同时存在类比/数位晶片的封装场合,且矽基、记忆体与射频元件等产品均适用。

此外,TSV的立体互连技术优势,也较打线接合的晶片连接型式有更多的技术优点。例如,具更短的内部互连路径、线路的电阻/电感值更低,亦可在传递讯号与晶片内的电力配送更具效率,甚至TSV制作方式另拥有可不限制裸晶堆叠数量,导入技术的优势相当显著,目前在CMOSSensor、记忆体产品已逐步导入TSV技术改善产品效能,此外在基频IC、射频IC与SoC处理器等应用领域,也会持续增加。

观察TSV制程现况,目前包含Via-first(先钻孔)及Via-last(后钻孔)两种技术实践方法,其中以后钻孔的技术困难度与挑战性较低,已较早导入相关产品应用,加上在晶片内线路制作的结构较大、亦较容易制做完成,对于业者来说也可以自SiP(SysteminaPackage)设计方法中延续制程技术进行封装法进阶改善,也吸引不少业者投入进行技术优化。

而先钻孔制程中必须将通道制作完成于其半导体制程之前,技术方面的难度较高,元件的制程构造本身就相当复杂,对形成通道作法难度更显困难,但实际上先钻孔制程可让通道线路品质更好,先钻孔制作方案具高传输效益,对于需要较高内部连接速度的高阶整合晶片设计需求,先钻孔有较高的使用附加价值。

评论