多方位多角度 带您重新诠释多核技术

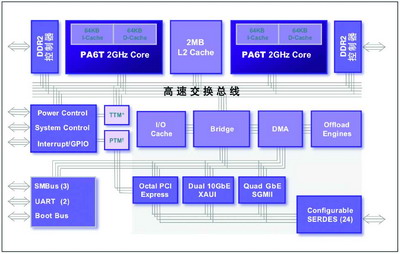

尽管PWRficient专门针对服务器应用,但它的设计思想对于X86产品仍然十分有借鉴意义。AMD计划在下一代处理器架构中引入类似的高度整合设计,直接内建PCI Express控制器,以提高系统的数据传输性能。事实上,整个芯片组的功能都可以被处理器所整合,这对于芯片组厂商而言显然不是什么好消息。

除了高度整合设计外,卓越的每瓦性能也是PWRficient处理器的主要卖点之一。PWRficient的核心频率为2GHz,芯片最高能耗区区25瓦,平均运行能耗甚至仅有5W的超低水平。IBM公司将重点放在高性能的Power 5/6和游戏机领域,对低功耗芯片重视不足,PWRficient便不会与IBM的产品有什么冲突。P.A.Semi公司将英特尔Sossaman核心的低功耗型Xeon作为主要对手,尽管Sossaman基于效率出众的Yonah架构,但它的能源效率远无法同PWRficient相提并论。

PWRficient 2GHz的实际性能略高于Sossaman Xeon 2.5GHz,但后者的能耗达到73瓦,整整比PWRficient高出两倍。对服务器系统而言,低功耗芯片的意义不仅在于散热更佳,最大的好处在于能够节约出可观的运营成本。P.A.Semi公司作出了详细的对比:如果要构建一套运算速度达到32TFLOPS标准的服务器集群,需要使用6400枚 Sossaman Xeon处理器,连带配套芯片组、万兆网卡等组件,整套集群的能耗将达到467200瓦;

而如果转用PWRficient平台,只需4000枚芯片就能够实现相同的性能,由于主要功能都被CPU直接集成,配套的芯片组也变得简单,整个集群的功耗只有92000瓦,相当于英特尔Sossaman Xeon平台的1/5,集群的空间占用、散热系统费用也更为低廉。如果选择PWRficient平台,集群系统的运营费用可以被大幅度削减,对本例的 32TFLOPS集群系统而言,就是每年可节约出至少100万美元运营费用,PWRficient的优势十分明显。

PWRficient将采用IBM的65纳米SOI工艺进行制造,P.A.Semi公司计划在下半年推出处理器样品,2007年正式上市。该芯片的主要销售对象包括服务器厂商、网络设备厂商,甚至还包括家电厂商,尤其在刀片服务器和服务器集群系统中,PWRficient具有明显的优势。但光有优秀的产品不足以说明问题,P.A.Semi只是一家小规模的技术型公司,自身没有服务器制造和推广力量,只有获得服务器厂商的支持才能够将 PWRficient推向实用化。而对IBM来说,既然没有更多的精力来开发低功耗Power芯片,将P.A.Semi收归旗下不失为一个好选择。

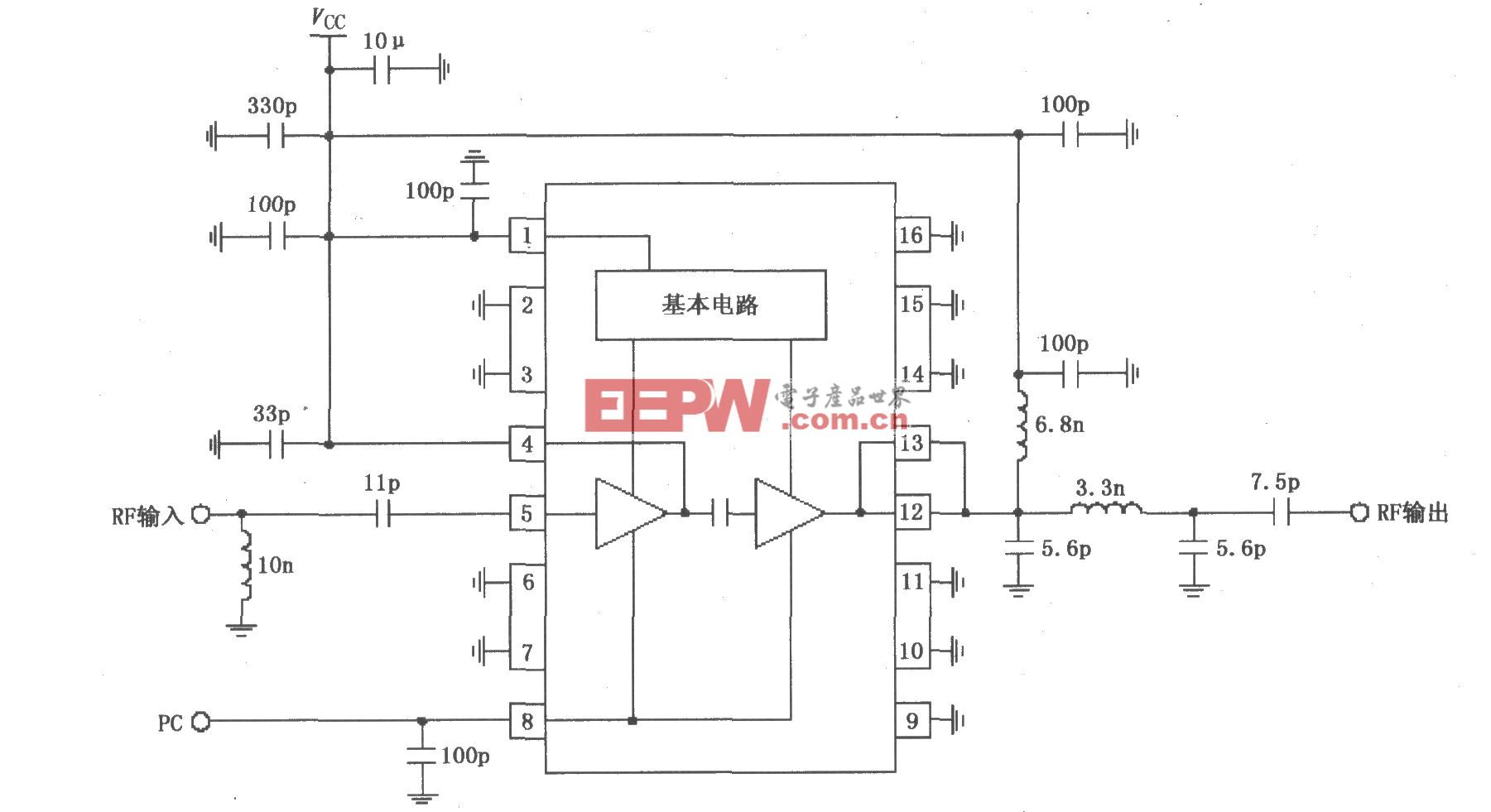

图1 PWRficient处理器的逻辑架构,整合了大量的I/O功能,堪称一款SOC(片上系统)型芯片。

精简核心和超多线程设计

SUN公司在2005年底推出的UltraSPARC T1也是微处理器领域的又一巅峰之作。同PWRficient的高度整合设计不同,UltraSPARC T1的重心放在多任务并行功能,这是由UltraSPARC T1自身的定位所决定的。UltraSPARC T1主要针对承担网络中枢的高端服务器系统,这类服务器主要面向高吞吐量的事务计算,需要在同时处理大量的并发任务,而这些任务又都不需要复杂的运算。

因此,SUN公司采用非均衡的思想来设计UltraSPARC T1:每个基本的CPU内核都相当精简,但都能够很好地完成相应的数据处理任务,由于精简核心占据的晶体管资源较少,处理器就能够集成更多的硬件内核;同时在较单纯的数据处理任务中,每个CPU核心的执行管线都不会被充分利用,在此基础上导入多线程技术将能够进一步提高系统的并行能力。我们可以看到,UltraSPARC T1拥有八个对等的硬件内核,每个内核可同步执行4个线程,这样仅仅一枚处理器就具备同时执行32个不同任务的能力。

UltraSPARC T1的晶体管总量只有3亿个左右,峰值能耗只有区区80瓦,执行效率相当出众。我们必须注意的是,UltraSPARC T1虽然具有超凡的事务处理能力,可它的科学计算能力十分糟糕,原因就在于SUN根据自身特殊的需要,采用不对等的设计。

UltraSPARC T1的CPU核心设计得非常简单,它的流水线很短,也没有包含浮点运算单元,只有在八个核心之外附加了一个浮点运算器。这样每个核心的晶体管占用就很少,为芯片低功耗奠定基础;UltraSPARC T1的每个核心均只运行在1.2GHz的低频率下,这也是拜短流水线设计所赐,芯片节能就不难理解了。UltraSPARC T1的每个核心都拥有16KB一级指令缓存和8KB的一级数据缓存,并具备奇偶检查能力(Parity Check),可以自行侦测缓存错误。

如果数据串中有1bit出现错误,缓存自身可对其进行修正,由此保证在苛刻环境下的运行可靠性。在二级缓存方面,UltraSPARC T1实行八核心共享的机制。由于核心数量众多,如果继续采用独立缓存设计的话,缓存同步操作需要耗费可观的运算资源,共享设计显然是更理想的选择。但为众多的核心分配缓存资源也是一个令人头疼的事情,SUN通过Crossbar连接架构来解决问题:八个核心在Crossbar的统一分配下获取缓存资源,有效避免了存取冲突。

一个比较特殊的地方就是UltraSPARC T1的二级缓存容量只有3MB,对一枚拥有八个硬件核心的处理器而言似乎少得可怜,但RISC处理器与X86处理器处理的任务迥异,提高缓存容量对X86 处理器的性能影响立竿见影,但UltraSPARC T1面向网络运算,而这类运算对缓存容量并不十分依赖,起到决定作用的是核心的性能。

多线程支持是UltraSPARC T1的一大亮点。UltraSPARC T1拥有一项名为CoolThreads的多线程技术,该技术令UltraSPARC T1的每个硬件核心都拥有同步执行4个线程的能力。这样,八核心的UltraSPARC T1可以在同一时间运行32个线程,具有超强的多任务处理能力。虽然英特尔的芯片很早就引入HyperTreading超线程功能、允许CPU执行两个线程,但HyperTreading设计僵化,线程一旦进入执行位置就无法替换,这样即便该线程耗费大量的执行资源和时间也必须持续等候。

在不少时候,此举反而会令系统的效能降低,这也是HyperTreading发展多年,但始终都没有获得广泛推行的主要原因。而SUN、IBM 等RISC处理器厂商在多线程技术领域有更深厚的实力,如IBM的Power 5系列具备线程动态转移功能,在线程运行开始即可对执行状况和资源使用进行实时侦测,如某个线程久拖不完或资源占用高,其余的核心又处于闲置状态时便立即将它转移,同时将运算资源和等候时间抚平,令系统保持卓越的并行执行效率。

评论