多方位多角度 带您重新诠释多核技术

在X86领域,英特尔和AMD在今后两年内还是会基于传统的多核心方案继续发展,其中,英特尔在下半年带来的Merom架构以高效率见长,但它非常缺乏扩展的空间;而AMD公司在未来两年内更多是对现有的AMD64架构进行改良。

本文引用地址://m.amcfsurvey.com/article/201609/304988.htm在过去数十年历史中,微处理器业界一直为提高芯片的运算性能而努力,得益于IC设计和半导体制造技术的交互拉动,微处理器的运算性能始终保持高速度提升状态,芯片的集成度、工作频率、执行效率也在这个过程中不断提升,计算机工业由此改变。在大家熟知的X86领域,处理器的技术进步更是对世界产生重大的影响,作为PC机的核心,X86处理器事实上担任起信息技术引擎的作用。

伴随着X86处理器的性能提升,PC机可以完成越来越多的任务:从最初的Basic到功能完善的DOS系统,再到图形化的Windows 95,从平面二维到3D环境渲染,从一个无声的纯视觉界面进入到视觉、音频结合的多媒体应用,计算机实现彼此相互联网,庞大的Internet日渐完善,电子商务应用从概念到全球流行;

与硬件技术高速发展相对应,PC应用也朝向前所未有的深度和广度拓展:视频媒体转向HDTV高清晰格式,3D渲染朝向电影画质进发,操作系统的人机界面也从2D的GUI进入到三维时代,高速互联网接入和无线技术方兴未艾,应用软件越来越智能化,所有这些应用都要求有高性能的处理器作为基础。而除了应用驱动外,激烈的市场竞争也成为微处理器业界竞相研发新技术、提高产品性能的主要推动力。

在2006年,我们将看到具有卓越能源效率的英特尔Merom架构出台,AMD则以双通道DDR2-800支持与之抗衡,同时双核心产品成为桌面和移动芯片的新标准,X86处理器进入到性能跃升阶段。

毋庸置疑,X86处理器已然成为计算机工业的主导力量,在高端服务器和嵌入领域广泛使用的RISC处理器反而少被提起。事实上,RISC处理器一直都以远超X86产品的卓越性能和锐意进取的技术创新著称,几乎所有先进的设计技术都是首先出现在RISC领域,之后才被X86产品所借鉴。而换一个角度来看,RISC处理器领域的每一次技术创新又反过来对X86产品产生重大影响,因此,了解当前RISC领域的尖端技术便意味着能够明晰X86处理器的未来走向。

今天,微处理器全面转向多核心体系,无论RISC芯片还是X86芯片皆是如此,不过我们在本文中所要介绍的并不是人们熟知的双核心 Pentium D或者Athlon64 X2,而是当前多核微处理器领域的最新技术成果以及面向未来的新颖概念,它们包括RISC领域的黑马、P.A.Semi公司的PWRficient双核处理器,SUN公司推出的 UltraSPARC T1八核心处理器,英特尔公司Many Core计划的实质以及AMD正在考虑的HyperTransport协处理器架构。

在这同时,我们也将向大家介绍各微处理器厂商对未来技术发展的不同理解,以及软件业如何应对为多核平台编程的巨大挑战。

高度整合的架构

P.A.Semi公司的PWRficient处理器在去年微处理器论坛(MPF2005)上正式揭晓。对于P.A.Semi这个名字,相信所有人都感到陌生,这家专门从事RISC处理器设计的技术型企业成立于2003年,创始者都是微处理器业界的顶尖人物。其CEO曾负责Alpha服务器芯片和 StrongARM手持机芯片的开发;负责技术的副总裁科勒也曾从事Alpha芯片的开发,后来进入AMD公司帮助定义了Opteron芯片的架构;另一负责架构的副总裁皮特同样曾为Alpha架构服务,在DEC公司发生的数次并购中先后进入康柏、惠普和英特尔。

在MPF2005论坛上,P.A.Semi公司对外公布其设计的双核心PWRficient处理器,高度整合的设计令外界耳目一新,并兼具低功耗和高性能两大特性。该公司同时表示,PWRficient弹性的架构可被方便扩展到八核心或用于超级计算机系统,在高端服务器领域颇具竞争力。

在设计PWRficient之时,P.A.Semi面临的第一个问题就是指令系统的选择,X86无疑更加流行、市场更广阔,但该领域被英特尔、 AMD把持,机会有限,加上X86指令系统复杂低效,与PWRficient的高端定位相悖。P.A.Semi最终选择了IBM的Power架构,这样 PWRficient处理器便成为IBM Power大家族中的一个新成员。

但除此之外,PWRficient与IBM的Power芯片并没有太多的共同点,它拥有一套极富弹性的架构、高度整合以及低功耗特性。 PWRficient主要定位在刀片服务器和低运营成本的服务器集群,P.A.Semi公司将英特尔的Sossaman Xeon处理器(Yonah架构)作为主要的竞争对手。

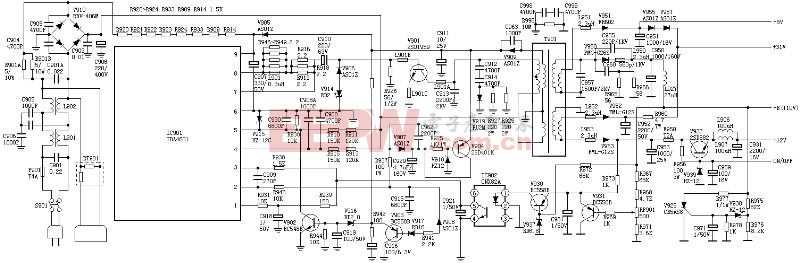

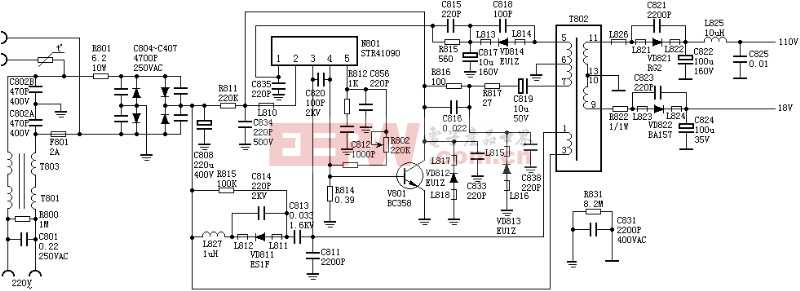

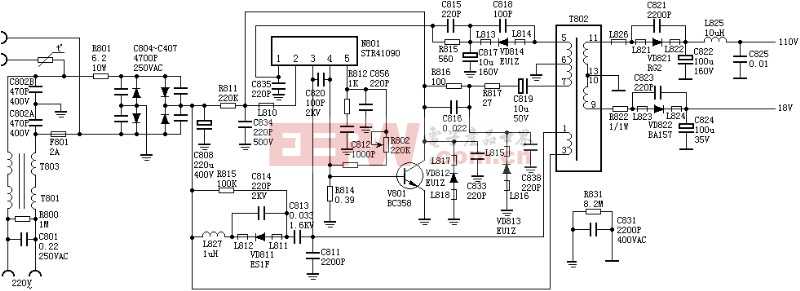

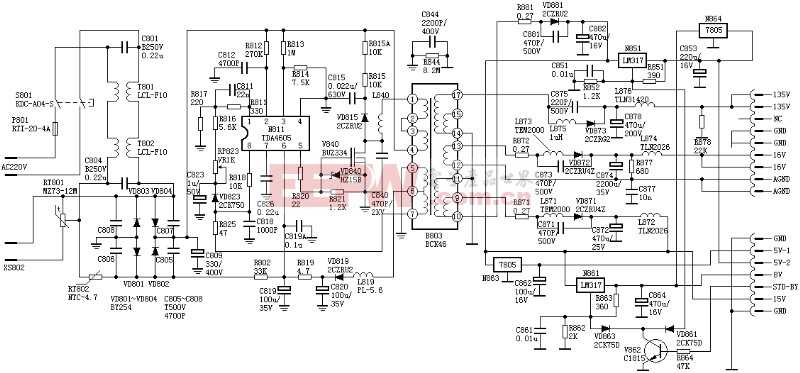

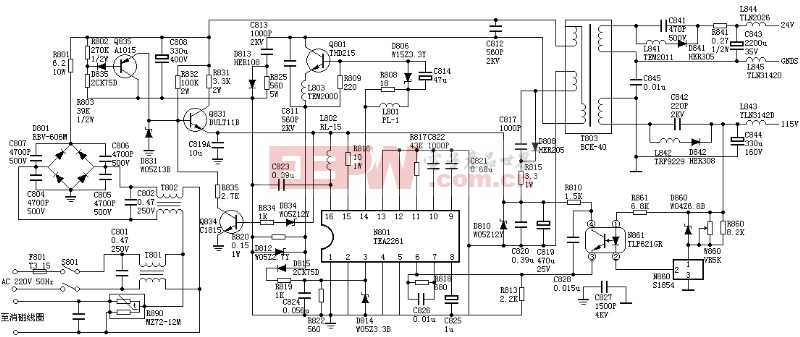

我们先来看看PWRficient的系统架构,如图1,我们可以看到,PWRficient与通常的处理器逻辑非常不同,除了CPU内核和二级缓存外,它还包括一个名为ENVIO的智能型I/O子系统。换句话说,PWRficient上包含CPU和ENVIO I/O子系统等两大逻辑,两者通过一个名为CONEXIUM Interchage的高速交换总线联结为一个有机系统。CPU部分为两个代号为PA6T的64位Power CPU内核,运行频率为2GHz。

与其他双核芯片不同的是,PWRficient的每一个 PA6T内核都拥有自己的DDR2内存控制器,但两者是以相互独立的模式而非组成共享的双通道。此种设计的好处在于每个CPU内核都能拥有属于自己的内存资源,最大限度降低内存抢占的几率。每个CPU内核都可支持64位或32位模式运作,具有诸如超标量、乱序执行、三发射等技术特性。另外,PA6T内核也都直接整合了硬件级的虚拟技术支持,可以在多套系统同时运行时仍保持出色的性能。

PA6T内核整合了64KB指令缓存和64KB数据缓存,而两个PA6T核心再共同分享2MB容量的二级缓存。PWRficient并没有采用类似Xeon的大缓存方案,原因就在于它的每个核心都有自己的内存,出现内存抢占的几率远低于共享总线的落后设计。

两个PA6T核心、2MB二级缓存和两个DDR2内存控制器都是通过CONEXIUM Interchage交换总线联结为一体,如果未来有需要,也可以在这条交换总线上联结四个内核甚至八个内核。但CONEXIUM的功能不仅于此,PWRficient处理器中的ENVOI I/O子系统也是通过这套总线与CPU逻辑直接通讯。与我们通常所见的固定模式不同,ENVOI相当灵活且富有弹性,它直接整合了八个PCI Express控制器(每个控制器提供4GBps带宽)、两个10GbE网络控制器(万兆以太网)和四个GbE(千兆以太网)控制器,这三部分I/O逻辑共享24对串行传输线路。

设备制造商可根据自身情况对这24对串行线路进行灵活配置,例如在NAS网络存储系统中,可以让连接磁盘系统的PCI Express传输获得更多线路资源,如果需要多端口的网络访问,那么便可以将线路资源朝向10GbE和GbE系统倾斜。这种高度弹性的架构让制造商拥有宽松的设计空间,可以根据企业的不同需要定制出最科学的服务器系统。而这种高度整合设计还有一个益处在于:无论是PCI Express系统还是网络系统,数据传输时的总线延迟都极短,进而获得卓越的数据传输效能。

评论