多方位多角度 带您重新诠释多核技术

可以预见,倘若继续沿着现有的通用、多核设计方案向前发展,X86处理器将会陷入一系列的困境,例如芯片高度复杂,开发和制造成本越来越高、芯片功耗无法控制等等。面对这样的现实,X86业界转变思想势在必行。显然,IBM Cell的新颖设计非常值得参考,英特尔的Many Core和AMD HyperTransport协处理器计划可以视作Cell思想的变种。

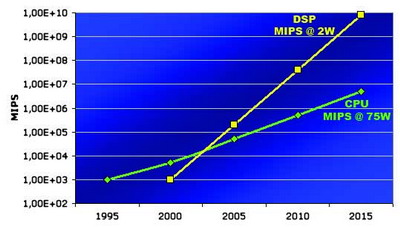

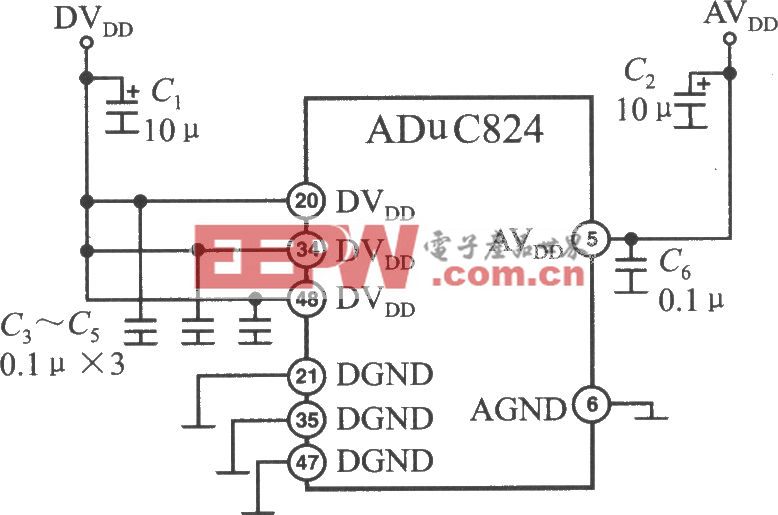

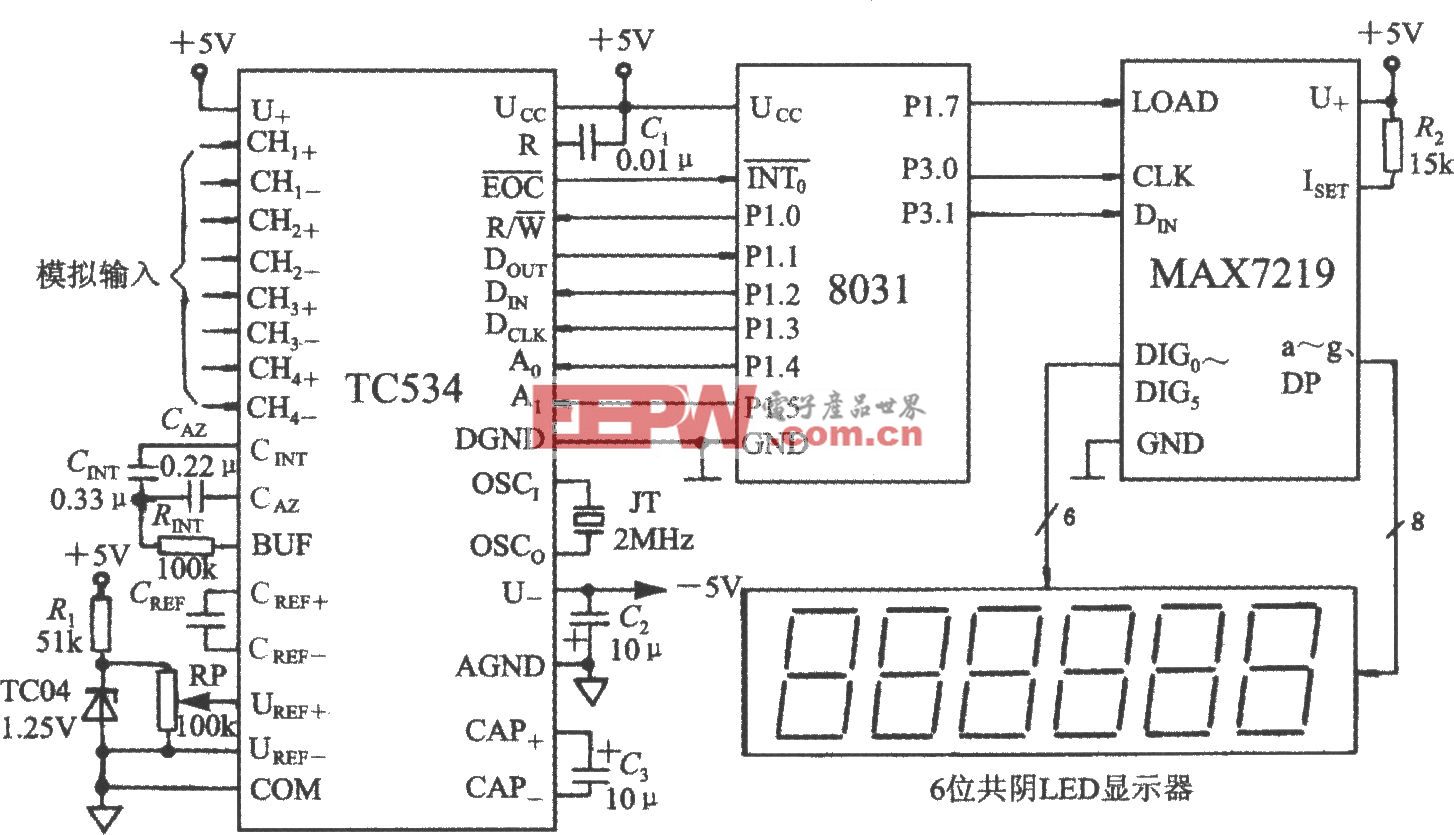

图4 DSP与通用CPU执行专用任务时的效能和效率对比

Many Core:Cell思想的继承与发展

在2005年的IDF技术峰会上,英特尔对外公布了Many Core超多核发展蓝图。随着时间推移,Many Core计划越来越明晰,我们可以肯定它将成为英特尔未来的X86处理器架构。Many Core采用的也是类似Cell的专用化结构,我们知道,英特尔的四核心处理器采用对等设计,每个内核地位相同,而转到Many Core架构之后,其中的某一个或几个内核可以被置换为若干数量的DSP逻辑,保留下来的X86核心执行所有的通用任务以及对特殊任务的分派;DSP则用于某些特殊任务的处理。

依照应用不同,这些DSP类型可以是Java解释器、MPEG视频引擎、存储控制器、物理处理器等等。在处理这类任务时,DSP的效能远优于通用的X86核心,功耗也低得多。在图4中我们可以看到DSP与通用CPU的效率对比:功耗仅2瓦、特定功能的DSP芯片,在处理对应任务时的效能比75瓦功耗的通用CPU更加出色,且由于DSP构造简单、频率提升非常容易;由于DSP效能提升速度比通用处理器快得多,这样随着时间的推移,DSP的效能优势将越来越明显。

而如果处理器将高负载的专用任务转交给DSP执行之后,那么主核心的运算压力就大大减轻,系统整体效能将获得明显提升。

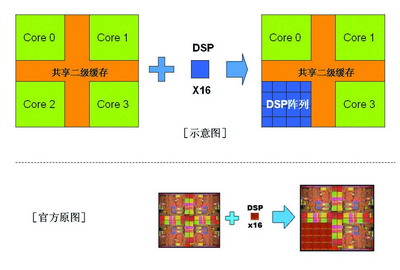

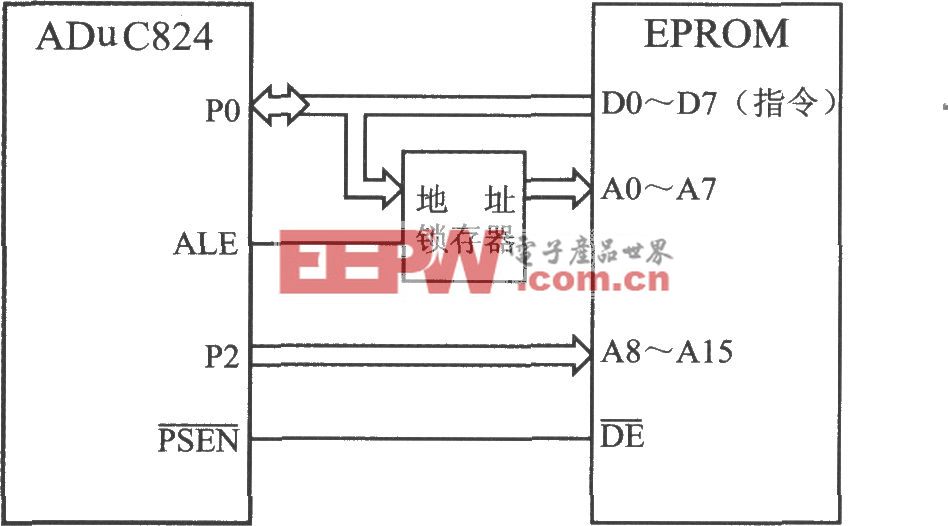

第一代Many Core架构处理器可能采用“3个通用X86核心+16个DSP内核”的组合(图5),我们可以看到,它的原型是一枚四核心处理器,只是将其中一个核心置换成16个DSP逻辑而已,因此处理器的总体结构和晶体管规模都不会有多大变化,但产品的实际水准将获得大幅度增强。在执行Java程序、视频解码、3D 渲染等耗用CPU资源的任务中,DSP的效能都大幅优于通用核心,因此Many Core产品在执行这类专用任务时会有飞跃性的性能增益。

同时,DSP逻辑的能耗只有通用核心的几十分之一,可以让处理器的功耗出现可观的降低。当然,如果我们将英特尔的Many Core处理器与Cell相比,便会发现一个明显的差异:Cell的主核心非常简单,协处理器则非常强大;而Many Core的通用核心仍然居于主导地位,DSP更多只是一种辅助。

这种差异源自于二者不同的定位:Cell只要求具备强劲的浮点效能,而对整数运算不作要求,因此通用的主核心可以非常精简;但Many Core必须考虑兼容大量的X86应用软件,专用的任务居于从属性地位,在第一代产品中采用“三个通用核心+16个DSP核心”的组合应该是比较恰当的。

根据英特尔的远景规划,第二代Many Core产品将在2015年前后面世。这当然过于遥远了,但我们不妨来看看它是一款什么样的产品(图6)—拥有8个通用X86核心、64个专用DSP逻辑,片内缓存容量高达1GB,晶体管规模则达到200亿。受限于半导体工艺,后两个目标或许很难完全实现,但Many Core设计将毋庸置疑成为标准,而英特尔从这往后将逐步引入Many Core Array架构,不断增强DSP的数量以及执行能力,通用核心的地位将随着时间推移不断减弱,直到最后完全可能实现以DSP占主导地位的专用化运算模式。

图5 从四核心平滑升级到“三核心+16DSP”的方案,即将其中一个通用核心置换成DSP阵列。

HyperTransport协处理器系统

在英特尔对Many Core概念作出具体探讨之时,AMD也在考虑自己的未来处理器架构。但与英特尔不同的是,AMD尚未考虑另起炉灶的Many Core计划,而是利用现有的HyperTransport连接架构,对多路服务器系统进行拓展。

Cray公司(克雷,著名的高性能计算机制造商)希望能在基于Opteron的超级计算机中使用矢量处理单元,以提升计算机的矢量运算效能。 AMD方面并不是简单考虑在Opteron核心中增加一个矢量逻辑了事,而是计划以此为契机,建立一个以AMD为中心的企业生态圈—这或许过于抽象,但看完下文的分析之后大家便能够明了其中的含义。

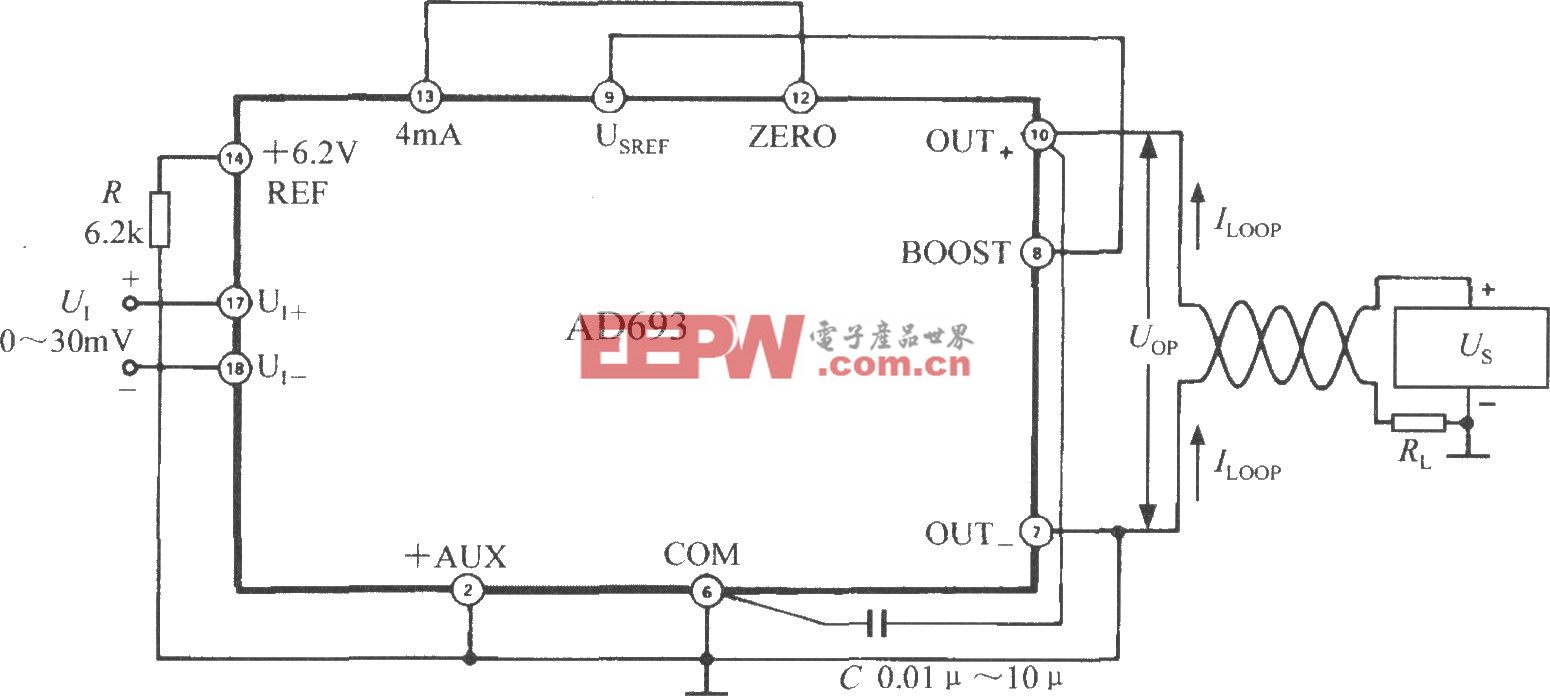

我们知道,现有的Opteron多路系统并非采用共享前端总线的方式连接,而是借助专用的HyperTransport总线实现芯片间的直连。这样,每一颗Opteron处理器都可以直接与其他的处理器进行数据交换或缓存同步,不必占用内存空间,无论系统中有多少数量的Opteron,整套系统都能够保持高效率的运作。在该套平台中,HyperTransport总线处于中枢地位,而它除了作为处理器连接总线外,还可以连接PCI-X控制器、 PCI Express控制器以及I/O控制芯片,也就是充当芯片间的高速连接通路。

AMD公司考虑的一套协处理器扩展方案也是以此为基础,即为多路Opteron平台开发各种功能的协处理器,这些协处理器都通过 HyperTransport总线与Opteron处理器直接连接。对Cray提出的需求,AMD给出的解决方案就是,将八路Opteron中的一颗 Opteron处理器置换成矢量协处理器,以此实现矢量计算性能的大幅度增长,而Opteron平台本身不需要作任何形式的变动。

在未来,这种拓展架构也可以延伸到PC领域,例如在PC中挂接基于HyperTransport总线的浮点协处理器、物理协处理器、视频解码器、专门针对Java程序的硬件解释器,甚至可以是由nVIDIA或ATI开发的图形处理器。为达成上述目标,AMD必须设计出一个高度稳定的统一接口方便用户进行扩展,而借助各种各样的协处理器,AMD64系统的性能将获得空前强化。

如果从逻辑层面来看,AMD HyperTransport协处理器系统的实质与英特尔Many Core平台其实完全相同,两者的区别更多是在物理组成方式:Many Core将专用的DSP逻辑直接整合于处理器内部,AMD的协处理器系统则是借助HyperTransport总线在外部挂接,这样用户就不必为了获得额外的性能购买新机,直接选择相应的协处理器挂接即可。由于协处理器类型将会非常丰富,每个用户都能从中找到最适合自己的产品,这在无形之中增强了AMD HyperTransport协处理器平台之于Many Core平台的竞争力。

评论