多方位多角度 带您重新诠释多核技术

UltraSPARC T1的 CoolThreads技术也具有类似的动态转移功能,任何一个执行单元有空余时,都可抓取已排入其他位置的待处理线程加以执行,由此维持八个核心的均衡负载。

UltraSPARC T1的整合内存控制器相当强大,它并不是像常规多核处理器一样只内建1组,而是拥有多达4组内存控制器,每个控制器都可以支持双通道ECC DDR2-533MHz内存、传输位宽达到144bit。在运行过程中,如果有4bit以下的内容错误,UltraSPARC T1的内存控制系统可自行纠正,如果错误数量提高到8bit,UltraSPARC T1仍然具备识别能力,系统可保持长时间的稳定运作。

另外,每组内存控制器都可以连接4个DIMM内存槽,因此一枚UltraSPARC T1处理器最多可管理多达16个DIMM模组,创造该领域的最高记录。毋庸置疑,UltraSPARC T1以4组144bit内存接口来对应8核心已经是相当充足,但SUN提供了更多的选择。在必要时候,用户可以将每两个控制器捆绑在一起,相当于将原本相互独立的4组内存系统变成两组可并行存取的结构,从而将内存系统的传输速度提高一倍。倘若系统执行的任务对数据传输有很高的要求,开启这项功能将对系统性能提升起到立竿见影的作用。

而在多路扩展方面,UltraSPARC T1采用的是SUN独有的JBus高速互联总线,JBus 1.0规格早在2003年4月就发布,采用128bit位宽的地址/数据接口,总线频率在150MHz-200MHz之间,峰值传输速率可达到 3.1GBps。虽然成就远不如AMD的HyperTranspot总线,但JBus的性能同样可满足多处理器数据交换的要求,毕竟UltraSPARC T1拥有八个核心和32个独立线程,处理器之间不需要交换太多的数据。

除了八核心版本外,SUN公司还将推出较低定位的六核心、四核心UltraSPARC T1,但三者其实都出自相同的晶圆,只是将存在瑕疵、但关闭部分内核后可正常运行的芯片作为六核或四核型号。令人惊讶的是,UltraSPARC T1非常节能,在八核心、32个线程都激活状态下的典型功耗仅有72瓦,峰值功耗也只有80瓦,能源利用效率极其出色;另外,UltraSPARC T1还可以通过关闭某些核心来达到节能的目的。

当然,我们不能简单将UltraSPARC T1与X86处理器作直接的对比,毕竟两者面向不同的应用、设计思想迥异。但从UltraSPARC T1中我们可以接触到另外一种设计思想:即根据特定的应用来设计处理器,使得该处理器能够在既定应用中获得最佳的效能。这种思想在RISC业界已经开始风行,X86处理器受通用所累,暂时难以实现类似设计,但在未来我们不排除这种思想被X86业界借鉴的可能:例如英特尔/AMD可以专门针对游戏玩家和多媒体娱乐用户设计出强化浮点性能的娱乐型处理器,或者设计出强化整数性能、功耗更低的办公型处理器,这样办公用户不必为自己不需要的浮点性能多掏腰包,娱乐用户也能够获得性能更出色的产品。而对英特尔、AMD厂商来说,只要设计一个富有弹性的处理器架构,制造出不同定位的产品并不需要花费多少代价。

专用协处理器实现效能跨越

PWRficient的高度整合思想、SUN UltraSPARC T1根据任务定制的精简核心、多任务方案令人耳目一新,但这两者其实都只是在现有多核架构基础上的革新,处理器本身仍然基于对等的多核心设计。

微处理器领域真正意义的架构革命将在未来数年内诞生,那就是多核架构将从通用的对等设计迁移到“主核心+协处理器”的非对等设计,亦即处理器中只有一个或数个通用核心承担任务指派功能,诸如浮点运算、HDTV视频解码、Java语言执行等任务都可以由专门的DSP硬件核心来完成,由此实现处理器执行效率和最终性能的大幅度跃进—IBM Cell、英特尔Many Core和AMD HyperTransport协处理器平台便是该种思想的典型代表。

下面,我们便从Cell入手,向大家介绍这种极具前途的新颖设计。

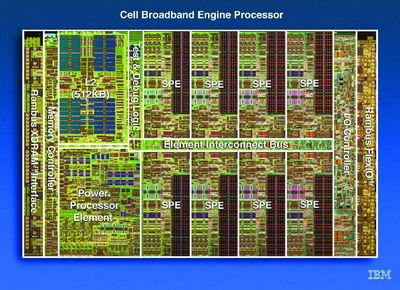

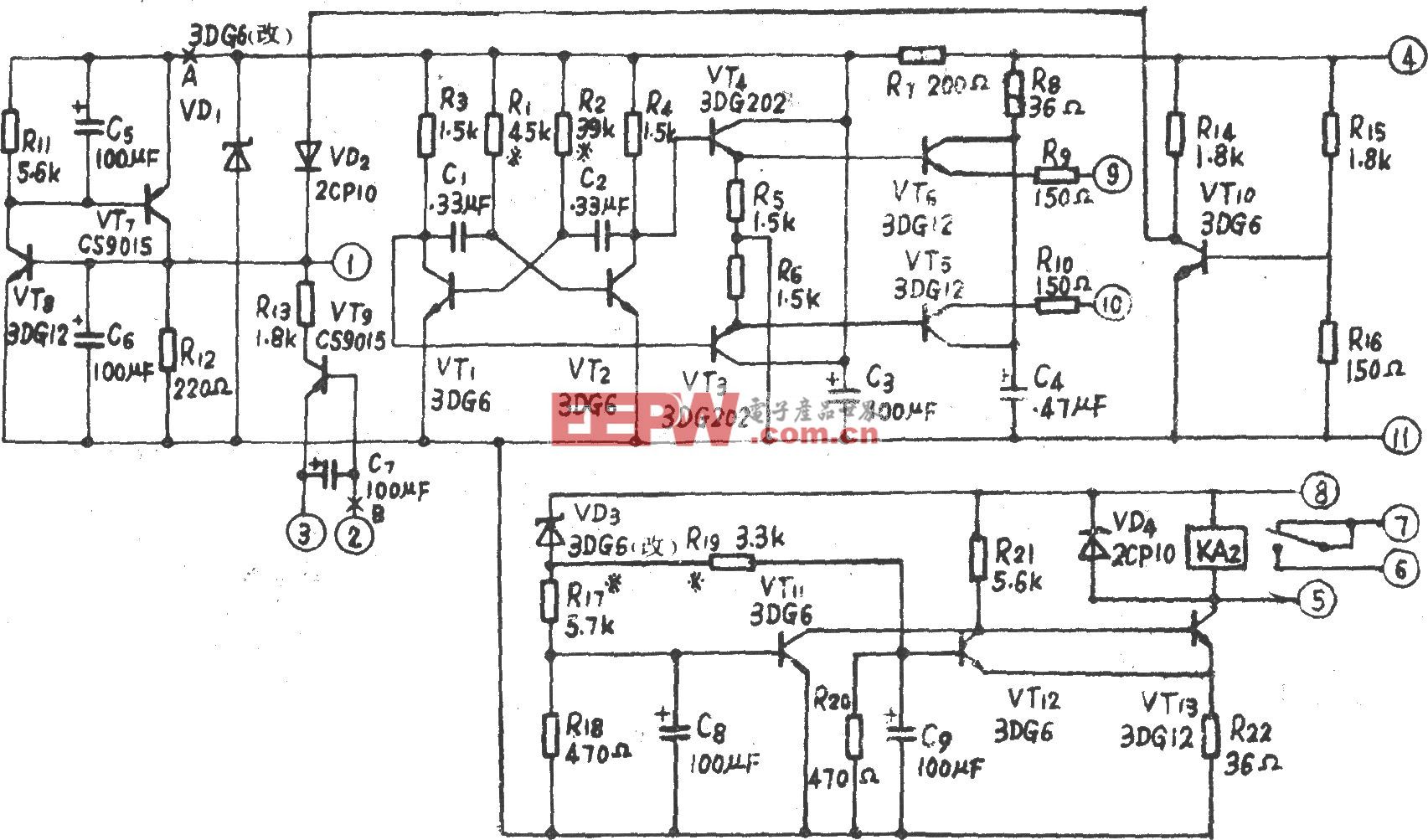

图3 Cell处理器基于“PPE主处理单元+SPE协处理器”的专用化设计,实现浮点性能的飞跃。

IBM Cell:开创全新的多核架构

IBM为索尼PS3游戏机定制的Cell是一枚拥有9个硬件核心的多核处理器,它的多核结构同以往的多核心产品完全不同。在Cell芯片中,只有一个核心拥有完整的功能,被称为主处理器,其余8个核心都是专门用于浮点运算的协处理器。其中,主处理器只是PowerPC 970的精简版本,其主要职能就是负责任务的分配,实际的浮点运算工作都是由协处理器来完成。

由于Cell中的协处理器只负责浮点运算任务,所需的运算规则非常简单,对应的电路逻辑同样如此,只要CPU运行频率足够高,Cell就能够获得惊人的浮点效能。而由于电路逻辑简单,主处理器和协处理器都可以轻松工作在很高的频率上—Cell起步频率即达到4GHz就是最好的证明。在高效率的专用核心和高频率的帮助下,Cell获得了高达256Gigaflops(2560亿次浮点运算每秒)的浮点运算能力,接近超级计算机的水准,远远超越目前所有的X86和RISC处理器。

作为对比,英特尔的4路Montecito安腾(双内核)系统也仅获得45Gigaflops的浮点性能。更令人惊讶的是,Cell只花费了区区2.34亿个晶体管,功耗在80-100瓦左右,能源利用效率比现在设计最佳的RISC和X86处理器都高出数十倍,这足以说明Cell专用、多核设计思想的优越性。

必须提到的是,Cell并非通用的处理器,虽然它具有极强悍的浮点运算性能,可很好满足游戏机和多媒体应用,但整数性能和动态指令执行性能并不理想,这是由任务的形态所决定的。未来耗费计算机运算性能最多的主要是3D图形、HDTV解码、科学运算之类的应用,所涉及到的其实都是浮点运算,整数运算只是决定操作系统和应用软件的运行效能(操作系统、Office软件等),而这部分应用对处理器性能要求并不苛刻,因此Cell将侧重点放在浮点运算性能,与SUN UltraSPARC T1专注事务处理的设计可以说有异曲同工之妙。

相较而言,当前的X86处理器都采用通用的核心,为了同时提高整数性能和浮点性能,CPU核心被设计得越来越臃肿,晶体管消耗越来越多,不仅导致芯片的功耗急剧增大,频率提升速度也非常缓慢。而且通用设计的另一个弊病在于,不管执行什么任务,芯片内的所有逻辑单元都消耗电力,导致X86芯片普遍存在能源利用率低的问题。

评论