多方位多角度 带您重新诠释多核技术

HyperTransport协处理器方案最富杀伤力的地方并非在于灵活性,而在于AMD所创建的“共生模式”。AMD计划将 HyperTransport协处理器授权给其他的专业IC设计公司,这样大量的第三方公司都可以为AMD64平台开发协处理器并分别销售,AMD自身只需要负责通用处理器的开发和HyperTransport原生态的维护。基于共同的利益,大量的第三方IC设计公司将紧密围绕AMD公司共同发展 HyperTransport平台:通过销售协处理器,第三方IC公司能够获得丰厚的回报,AMD则通过平台授权和AMD64处理器的销售获得利润、并在第三方公司的帮助下提高市场份额。

至于终端用户,则可以在现有基础上通过增加或升级协处理器达成大幅度提高系统性能的目的—这便是AMD倡导的“友好生态系统”的实质。与AMD 的开放策略形成鲜明对比,英特尔将变得越来越封闭,从迅驰到VIIV平台,第三方厂商的机会越来越少,英特尔希望将全部的商业利润都归自己所有,而不是与合作厂商共同分享机会。在这样的背景下,越来越多IC厂商转向对AMD平台的支持,因此AMD所倡导的友好生态系统其实已经有相当良好的基础。

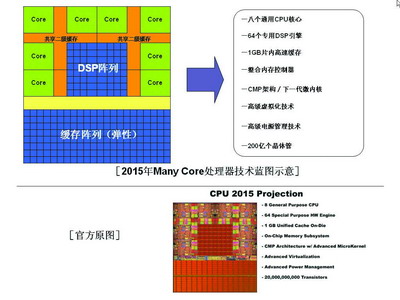

图6 2015年的处理器蓝图,Many Core设计成为标准

前瞻:架构革命的前夜

尽管X86业界依然按部就班地进行性能提升,软件工业也是在以往基础上匍匐前进,但这场架构革命距离我们并不遥远。在RISC领域,针对实际应用对产品作定制化设计成为各个厂商的共识,而各个厂商在开发新一代架构时都会有意识地为处理器预留扩展定制的空间。

相信在未来,我们可以看到越来越多的专用型RISC处理器,例如游戏机/视频任务处理器、网络处理器、低耗能通用处理器、嵌入处理器等等;而在 X86领域,英特尔和AMD在今后两年内还是会基于传统的多核心方案继续发展,其中,英特尔在下半年带来的Merom架构以高效率见长,但它非常缺乏扩展的空间;到2008年,英特尔才会陆续引入CSI总线并整合内存控制器,解决多路服务器系统扩展性的问题;大约到2010年,我们有望看到第一代Many Core处理器出台,X86处理器将转向一个全新的多核时代。

而AMD公司在未来两年内更多是对现有的AMD64架构进行改良,例如引入双通道DDR2-800支持和65纳米SOI工艺,服务器领域 Opteron的优势不太容易被打破。大约在2008年,AMD将带来新一代的K9或K10,高度整合设计将被引入,更关键的是,AMD将带来 HyperTransport 3.0和4.0版总线技术规范,并有可能开始启动协处理器计划。

由于HyperTransport 3.0/4.0将直接对协处理器提供支持,AMD只需要解决主处理器与协处理器的任务协作以及硬件连接标准的制定即可,接下来的协处理器开发工作便主要依靠第三方IC公司加以实现。如果AMD在新一轮变革中再度领先,那么在大量第三方企业和用户的支持下,英特尔在微处理器市场的主导优势很可能彻底丧失,最终出现两大平台分庭抗礼的格局。

当前微处理器技术发展的几个方向

提高架构执行效率、多核心设计、灵活的扩展弹性、深层次的功能整合是当前微处理器领域的四大技术发展方向。处理器效率低下的弊端主要出现在 X86领域,X86指令集臃肿复杂,指令效率已明显低于RISC体系,如果不在芯片设计方面加以弥补,X86处理器很难获得媲美RISC产品的卓越性能。

衡量处理器效率通常有两个指标:一是芯片的能源利用效率,也就是每瓦性能,在消耗同等能源条件下,最终性能高的产品能源效率就较高;第二个指标便是芯片的晶体管效率,我们可以引入“每晶体管性能”来衡量,在消耗等量晶体管数量条件下,芯片效能高者效率就越高。

晶体管规模越大,制造成本越高,对芯片厂商来说,提高每晶体管性能能够在保持成本不变的前提下获得更卓越的性能。一般来说,每瓦性能和每晶体管性能总是被结合起来讨论,不同指令体系的产品在此相差甚远,例如当前顶级的RISC处理器与顶级的X86处理器作对比,我们便会发现X86芯片远远落后。

即便基于相同的指令体系但设计不同的产品,也可能存在悬殊的效率差异—一个最典型的例子就是英特尔Netburst架构与AMD64架构,Pentium 4芯片的功耗更高,晶体管规模也普遍更大,但性能无法同对应的AMD64架构产品抗衡。且Pentium 4芯片的能耗已超过百瓦,达到风冷散热的极限,无法进一步向上提升。

为了解决这个问题,英特尔将在今年中期引入Merom架构来代替Netburst,诚如我们之前的分析,Merom引入了RISC精简指令的思想,对X86架构进行根本性的改进得以大幅提高效率。而在RISC技术领域,提高效率也一直都是各制造商的目标,虽然RISC芯片在这方面已占据先天优势,但各芯片厂商仍然在此方面花费巨大的精力并获得斐然成果。在本文关于P.A.Semi的PWRficient双核处理器、SUN UltraSPARC T1八核处理器的分析中,我们将能看到这一点。

多核心设计可谓是提高每晶体管效能的最佳手段。在单核产品中,提高性能主要通过提高频率和增大缓存来实现,前者会导致芯片功耗的提升,后者则会让芯片晶体管规模激增,造成芯片成本大幅度上扬。尽管代价高昂,这两种措施也只能带来小幅度性能提升。而如果引入多核技术,便可以在较低频率、较小缓存的条件下达到大幅提高性能的目的。相比大缓存的单核产品,耗费同样数量晶体管的多核心处理器拥有更出色的效能,同样在每瓦性能方面,多核设计也有明显的优势。

正因为如此,当IBM于2001年率先推出双核心产品之后,其他高端RISC处理器厂商也迅速跟进,双核心设计由此成为高端RISC处理器的标准。而X86业界直到去年中期才开始尝试推出双核产品,预计实现全面普及要等到2006-2007年。

此时,RISC业界又朝向多核、多线程的方向发展,四核心、八核心设计纷纷登台亮相,并行线程数量多达32条,并且开始从通用多核体系转向简化核以及专用化的DSP,实现性能的跨越性提升—这些新设计和新方向也都将被X86业界所借鉴。

评论