西门子与SPIL合作为扇出型晶圆级封装打造3D验证流程

西门子数字化工业软件日前与矽品精密工业股份有限公司(矽品,SPIL) 合作,针对SPIL的扇出型系列先进 IC 封装技术开发并实施新的工作流程,以进行 IC 封装装配规划以及 3D LVS (layout vs. schematic) 装配验证。该流程将应用于SPIL的 2.5D 和扇出型封装系列技术。

本文引用地址://m.amcfsurvey.com/article/202306/447639.htm

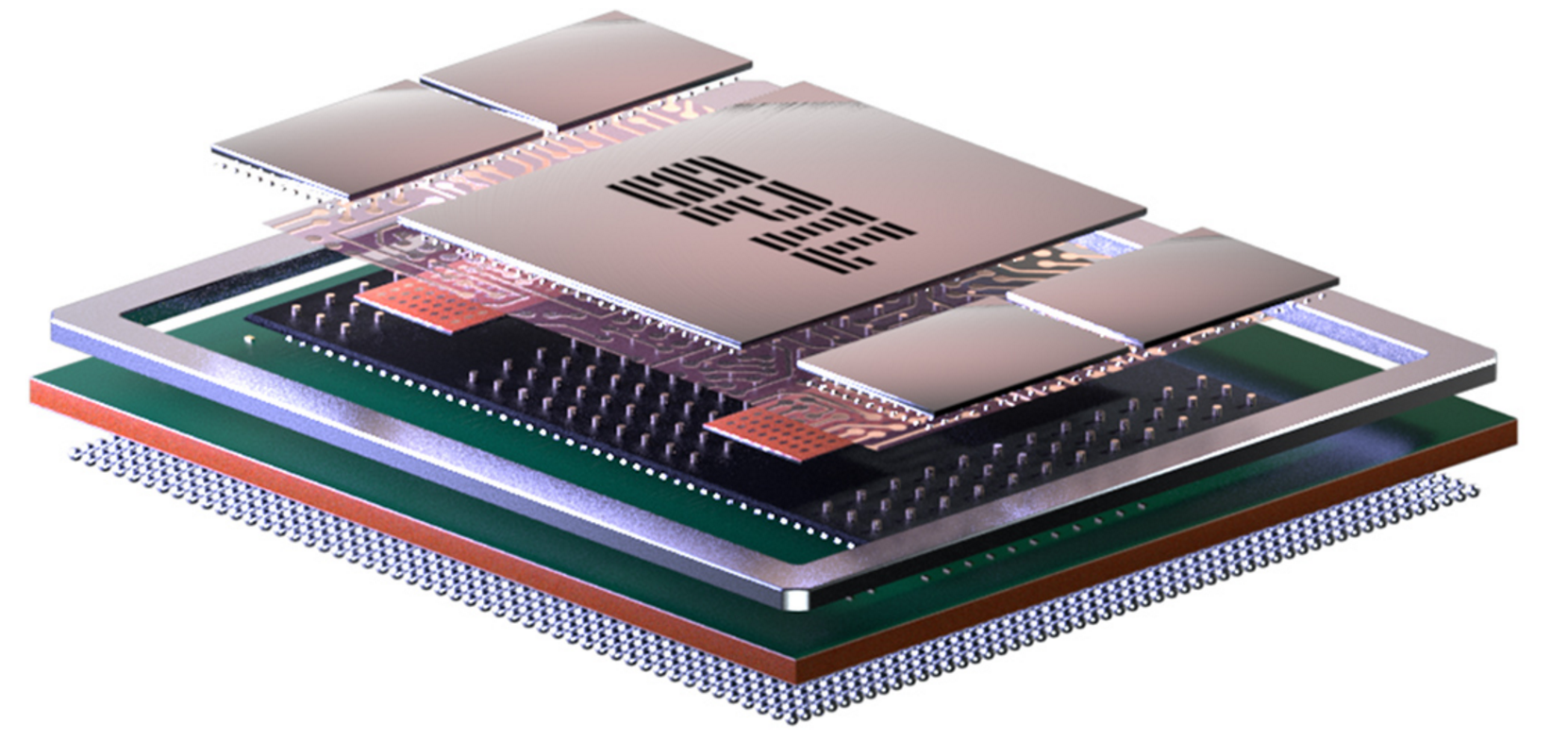

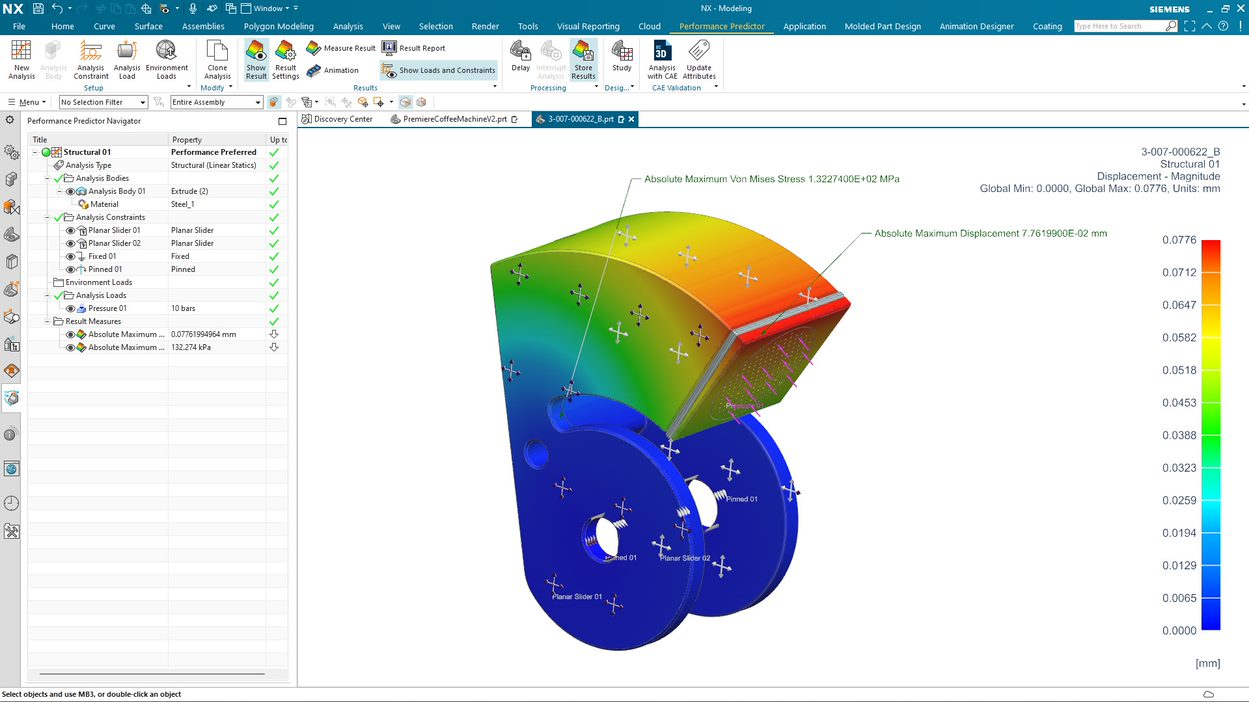

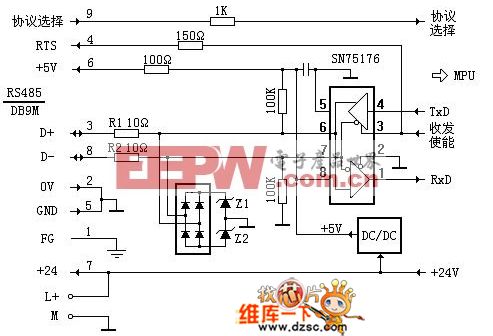

为了满足市场对于高性能、低功耗、小尺寸 IC 的上扬需求,IC 设计的封装技术也变得日益复杂,2.5D 和 3D 配置等技术应运而生。这些技术将一个或多个具有不同功能的 IC 与增加的 I/O 和电路密度相结合,因此需要创建并查看多个装配和 LVS、连接关系、几何形状和元件间距场景。为了帮助客户轻松实施这些先进的封装技术,SPIL 采用西门子的 Xpedition™ Substrate Integrator 软件和 Calibre®3DSTACK 软件,用于其扇出系列封装技术的封装规划和 3D LVS 封装装配验证。

矽品精密工业股份有限公司研发中心副总王愉博博士表示:“矽品着力于开发和部署一套经过验证且包括全面 3D LVS 的工作流程,以进行先进封装装配规划和验证。西门子是该领域公认的领导厂商,拥有稳健的技术能力并获得市场的广泛认可。矽品将在今后的生产中使用与西门子共同打造的流程来验证我们的扇出系列技术。”

SPIL 的扇出型封装系列能够提供更大空间,在半导体区域之上布线更多的 I/O,并通过扇出型工艺扩展封装尺寸,而传统封装技术无法做到这一点。

西门子数字化工业软件电路板系统高级副总裁 AJ Incorvaia 表示:“西门子很高兴与 SPIL 合作,为其先进封装技术定义和提供必要的工作流程和技术。SPIL 的客户正努力探索更复杂的设计,SPIL 和西门子也随时准备为其提供所需的工作流程,将这些复杂设计加速推向市场。”

评论