- 全球电子设计创新领先企业Cadence设计系统公司(NASDAQ:CDNS)日前宣布推出全新用于PCIe 3.0的SpeedBridge® Adapter。它为设计师们提供了一个重要的工具,来验证和确认他们的PCI Express (PCIe) 设计。

- 关键字:CadencePCIeSoC

- 益华电脑(Cadence Design Systems)近日宣布两项成功合作案例,其一为设计服务业者创意电子(GUC)运用Cadence Encounter数位设计实现系统(Digital Implementation System,EDI)与Cadence Litho Physical Analyzer,成功地完成了20nm系统晶片(SoC)测试晶片的试产。此外晶圆代工大厂联电(UMC)已经采用Cadence 「设计中(in-design)」与signoff DFM (design-for-manufa

- 关键字:Cadence制程设计

- 全球电子设计创新领先企业Cadence设计系统公司(NASDAQ:CDNS)日前宣布,历经广泛的基准测试后,半导体制造商联华电子(NYSE:UMC;TWSE:2303)(UMC)已采用Cadence® “设计内”和“签收”可制造性设计(DFM)流程对28纳米设计进行物理签收和电学变量优化。

- 关键字:联华电子CadenceDFM

- 全球电子设计创新领先企业Cadence设计系统公司(NASDAQ:CDNS) 日前宣布推出用于实现电学感知设计的Virtuoso®版图套件,它是一种开创性的定制设计方法,能提高设计团队的设计生产力和定制IC的电路性能。

- 关键字:CadenceVirtuosoEAD

- 为专注于解决先进节点设计的日益复杂性,全球电子设计创新领先企业Cadence设计系统公司(NASDAQ:CDNS) 日前宣布,台积电已与Cadence在Virtuoso定制和模拟设计平台扩大合作以设计和验证其尖端IP。

- 关键字:CadenceVirtuoso台积PDKs

- 全球电子设计创新领先企业Cadence设计系统公司(NASDAQ:CDNS) 日前宣布,设计服务公司创意电子(GUC)使用Cadence® Encounter®数字实现系统(EDI)和Cadence光刻物理分析器成功完成20纳米系统级芯片(SoC)测试芯片流片。双方工程师通过紧密合作,运用Cadence解决方案克服实施和可制造性设计(DFM)验证挑战,并最终完成设计。

- 关键字:CadenceDFM

- Cadence Encounter数字实现系统与Cadence光刻物理分析器 可降低风险并缩短设计周期 全球电子设计创新领先企业Cadence设计系统公司(NASDAQ:CDNS) 今天宣布,设计服务公司创意电子(GUC)使用Cadence? Encounter?数字实现系统(EDI)和Cadence光刻物理分析器成功完成20纳米系统级芯片(SoC)测试芯片流片。双方工程师通过紧密合作,运用Cadence解决方案克服实施和可制造性设计(DFM)验证挑战,并最终完成设计。 在开发过程中

- 关键字:Cadence20纳米SoC

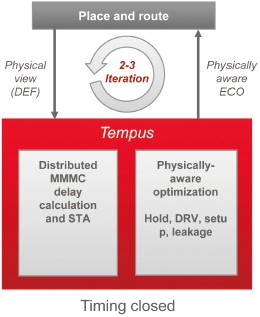

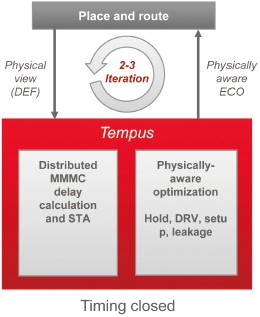

- 为简化和加速复杂IC的开发,Cadence 设计系统公司不久前推出Tempus时序签收解决方案。这是一款新的静态时序分析与收敛工具,旨在帮助系统级芯片 (SoC) 开发者加速时序收敛,将芯片设计快速转化为可制造的产品。

- 关键字:CadenceTempusCPU201307

- Cadence日前宣布,台积电(TSMC)在20纳米制程对全新的Cadence Tempus时序签收解决方案提供了认证。该认证意味着通过台积电严格的EDA工具验证过的Cadence Tempus 时序签收解决方案能够确保客户实现先进制程节点的最高精确度标准。

- 关键字:Cadence台积电Tempus

- 在加速复杂IC开发更容易的当下,益华电脑(Cadence Design Systems, Inc.)发表 Tempus 时序 Signoff解决方案(Timing Signoff Solution),这是崭新的静态时序分析与收敛工具,精心设计让系统晶片(System-on-Chip,SoC)开发人员能够加速时序收敛,让晶片设计更快速地投入制造流程。Tempus 时序Signoff解决方案意谓全新的时序signoff工具作法,让客户能够缩短时序signoff收敛与分析,实现更快速的试产,同时创造良率更高

- 关键字:CadenceSoC设计

- 为设计收敛和签收提供前所未有的性能和容量 Tempus?时序签收解决方案提供的性能比传统的时序分析解决方案提升了一个数量级。 可扩展性,能够对具有上亿个实例的设计进行全扁平化分析。 集成的签收精度的时序收敛环境利用创新的考虑物理layout的ECO技术,可以使设计闭合提前数周时间。 为简化和加速复杂IC的开发,Cadence 设计系统公司推出Tempus? 时序签收解决方案。这是一款新的静态时序分析与收敛工具,旨在帮助系统级芯片 (SoC) 开发者加速时序收敛,将芯片设计快速转

- 关键字:CadenceTempus时序签收

- 【中国,2013年5月14日】全球电子设计创新领先企业Cadence设计系统公司(NASDAQ: CDNS),近日推出新版本Incisive Enterprise Simulator,该版本将复杂SoC的低功耗验证效率提高了30%。13.1版的Cadence Incisive Enterprise Simulator致力于解决低功耗验证的问题,包括高级建模、调试、功率格式支持,并且为当今最复杂的SoC提供了更快的验证方式。 Incisive SimVision Debugger的最新

- 关键字:CadenceSoC

- 【中国,2013年5月13日】全球电子设计创新领先企业Cadence设计系统公司(NASDAQ:CDNS)近日宣布,GLOBALFOUNDRIES已携手Cadence®,为其20和14纳米制程提供模式分类数据。GLOBALFOUNDRIES之所以采用Cadence模式分类和模式匹配解决方案,是因为它们可以使可制造性设计(DFM)加快四倍,这对提高客户硅片成品率和可预测性非常关键。 “我们已集成了Cadence模式分类技术,根据模式相似性将成品率不利因素分成若干模式

- 关键字:Cadence28纳米

- 2013年3月11日,EDA领头羊Cadence宣布,其已与在数据平面处理(DPU) IP领域的领导者Tensilica以约3.8亿美元现金收购Tensilica达成协议。至此,Cadence在高速数据处理和接口IP方面布局已基本就绪,为下一代SoC设计做好了IP准备。

- 关键字:CadenceARMCPU201304

cadence介绍

EDA仿真软件Cadence -------------------------------------------------------------------------------- Cadence Design Systems Inc.是全球最大的电子设计技术(Electronic Design Technologies)、程序方案服务和设计服务供应商。其解决方案旨在提升和监控半导 [

查看详细]

关于我们-

广告服务-

企业会员服务-

网站地图-

联系我们-

征稿-

友情链接-

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473