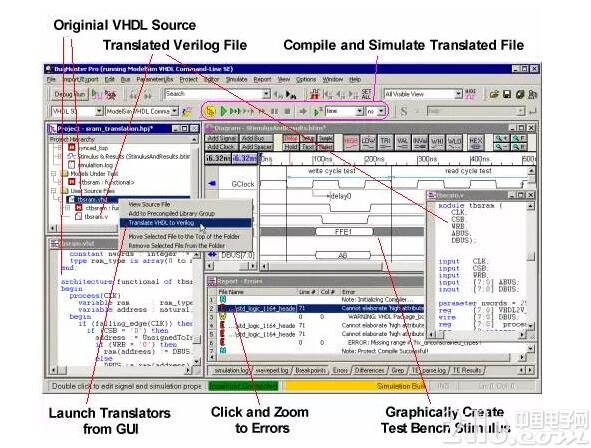

这两种语言都是用于数字电子系统设计的硬件描述语言,而且都已经是 IEEE 的标准。 VHDL 1987 年成为标准,而 Verilog 是 1995 年才成为标准的。这个是因为 VHDL 是美国军方组织开发的,而 Verilog 是一个公司的私有财产转化而来的。为什么 Verilog 能成为 IEEE 标准呢?它一定有其优越性才行,所以说 Verilog 有更强的生命力。

关键字:Verilog VHDL HDL

VHDL 语言的英文全名是 Very High Speed Integrated Circuit Hardware Description Language ,即超高速集成电路硬件描述语言。 HDL 发展的技术源头是:在 HDL 形成发展之前,已有了许多程序设计语言,如汇编、 C 、 Pascal 、 Fortran 、 Prolog 等。

关键字:VHDL

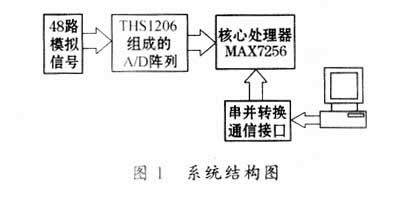

FPGA/CPLD 的设计思想与技巧是一个非常大的话题,由于篇幅所限,本文仅介绍一些常用的设计思想与技巧,包括乒乓球操作、串并转换、流水线操作和数据接口的同步方法。希望本文能引起工程师们的注意,如果能有意识地利用这些原则指导日后的设计工作,将取得事半功倍的效果!

关键字:设计思想 FPGA CPLD

电子设计自动化(EDA)的实现是与CPLD/FPGA技术的迅速发展息息相关的。CPLD/FPGA是80年代中后期出现的,其特点是具有用户可编程的特性。利用PLD/FPGA,电子系统设计工程师可以在实验室中设计出专用IC,实现系统的集成,从而大大缩短了产品开发、上市的时间,降低了开发成本。此外,CPLD/FPGA还具有静态可重复编程或在线动态重构特性,使硬件的功能可象软件一样通过编程来修改,不仅使设计修改和产品升级变得十分方便,而且极大地提高了电子系统的灵活性和通用能力。

关键字:可编程逻辑器件 FPGA CPLD 电子设计 灵活性

近年来,随着信息科技的发展,电子存包系统由于其安全性高、可靠性高、方便快捷等特点,在车站码头、超市、图书馆、宾馆、游泳馆、俱乐部等公共场所及机关、企事业单位文件档案管理等部门得到了广泛的应用,有着广阔的市场前景。

关键字:CPLD

CPLD(Complex Programmable Logic Device)是Complex PLD的简称,一种较PLD为复杂的逻辑元件。CPLD是一种用户根据各自需要而自行构造逻辑功能的数字集成电路。其基本设计方法是借助集成开发软件平台,用原理图、硬件描述语言等方法,生成相应的目标文件,通过下载电缆(“在系统”编程)将代码传送到目标芯片中,实现设计的数字系统。

关键字:CPLD

SOPC一词主要是源自Altera, 其涵义是因为目前CPLD/FPGA的容量愈來愈大, 性能愈來愈好, 加上价格下跌的推波助澜之下, 以往ASIC产品才能具有的 SoC观念, 也能移植到CPLD/FPGA上, 并且因为CPLD/FPGA的可编程(Programmable)能力, 使得CPLD/FPGA不仅能实现一个高复难度的系统, 而且还能快速改变系统的特性. 类似的观念也鉴于Xilinx的Platform FPGA.

关键字:SOPC CPLD FPGA

刚毕业的时候,我年少轻狂,以为自己已经可以独当一面,庙堂之上所学已经足以应付业界需要。然而在后来的工作过程中,我认识了很多牛人,也从他们身上学到了很多,从中总结了一个IC设计工程师需要具备的知识架构,想跟大家分享一下。 技能清单 作为一个真正合格的数字IC设计工程师,你永远都需要去不断学习更加先进的知识和技术。因此,这里列出来的技能永远都不会是完整的。我尽量每年都对这个列表进行一次更新。如果你觉得这个清单不全面,可以在本文下留言,我会尽可能把它补充完整。 语言类:Verilog-2001/&nb

关键字:IC设计 VHDL

Verilog HDL是硬件描述语言的一种,用于数字电子系统设计。它允许设计者用它来进行各种级别的逻辑设计,可以用它进行数字逻辑系统的仿真验证、时序分析、逻辑综合。它是目前应用最广泛的一种硬件描述语言之一。Verilog HDL是在1983年由GDA公司的Phil Moorby首创的。

关键字:VerilogHDL VHDL Verilog-XL 华清远见

智能温室是近年逐步发展起来的一种资源节约型高效农业发展技术,目前国内大多以单片机、通用计算机作为温室系统处理器,由于基于单因子和成本问题,其智能化和效率有待提高。在此通过对目前智能温室控制器的分析研究,提出并设计了一款16位的的单总线专用CPU,且专门针对于智能温室测控系统设计了一个浮点运算器和n个Comparray比较器,并使用VHDL

关键字:VHDL 温室控制系统 浮点运算器 Comparray比较器

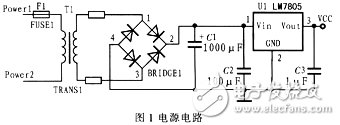

以MOS开关、电容器和运算放大器为核心的单片集成器件SCF,以其对截止频率的精确控制,频率响应特性可大范围调节,编程控制简单,有效解决了模拟滤波器的通带调节问题,在滤波电路设计中得到广泛应用。

关键字:SCF 程控滤波电路 CPLD

介绍了采用一种自主研发多功能IP核实现总线全地址响应的设计方案,其可在FPGA中灵活配置,配备外围电路后可以方便实现各种功能.设计采用VHDL硬件描述语言进行编程,采用综合工具ISE Foundation对设计进行综合、优化,在ModelSim - SE 6.1g中进行时序仿真,并且最后在FPGA上实现.

关键字:多功能IP核 VHDL ModelSim

基于FPGA设计了一款通用键盘IP核,该核主要实现对键盘输入信号的计算与存储功能,并在quartusⅡ环境下使用VHDL语言,采用自顶向下设计方式,编辑生成RTL原理图,并做了相关的时序仿真验证。经验证此IP核具有较强的鲁棒性和较高的反应速度,可作为基础输入模块,为其他模块提供有力控制输入与数据支持。

关键字:键盘IP核 VHDL FPGA

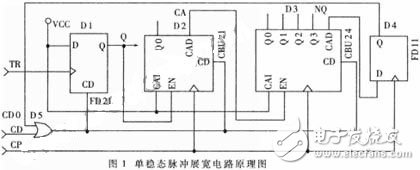

本控制仪以单片机80c196kc为核心,集无功补偿、电度量计量、电能质量监测及通信于一体,能实时显示电网的各项参数,通过键盘可人工设定系统运行的参数。单片机外围芯片PSD8XX及复杂可编程逻辑器件(CPLD)的使用不仅使系统的硬件电路简化,而且使系统的性能提高。本文将讨论用CPLD来实现控制仪的键盘系统,给出了硬件电路和软件设计方法。

关键字:键盘扩展 无功补偿装置 CPLD

vhdl-cpld介绍

您好,目前还没有人创建词条vhdl-cpld!

欢迎您创建该词条,阐述对vhdl-cpld的理解,并与今后在此搜索vhdl-cpld的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473