“芯”潮澎湃 揭秘集成电路的“庐山真面目”

第四阶段合影

本文引用地址://m.amcfsurvey.com/article/201705/359846.htm

光刻胶:再次浇上光刻胶(蓝色部分),然后光刻,并洗掉曝光的部分,剩下的光刻胶还是用来保护不会离子注入的那部分材料。

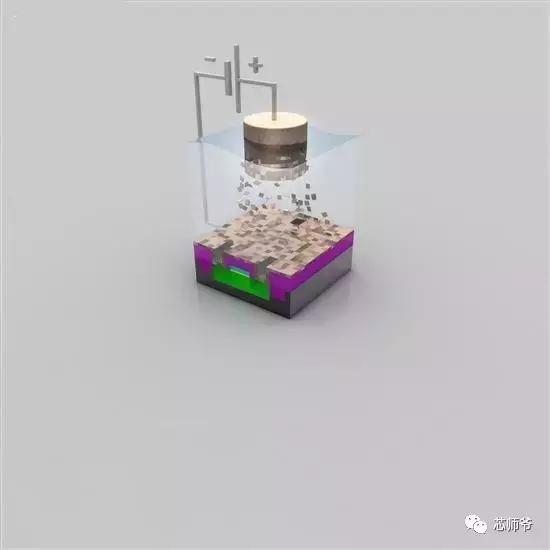

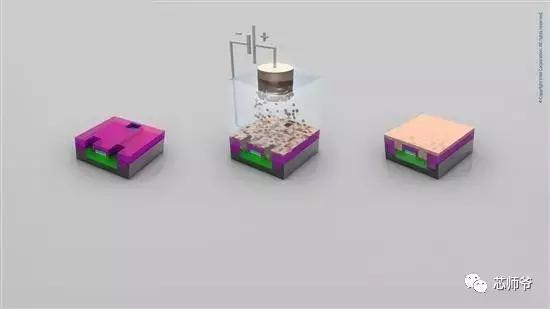

离子注入(Ion Implantation):在真空系统中,用经过加速的、要掺杂的原子的离子照射(注入)固体材料,从而在被注入的区域形成特殊的注入层,并改变这些区域的硅的导电性。经过电场加速后,注入的离子流的速度可以超过30万千米每小时。

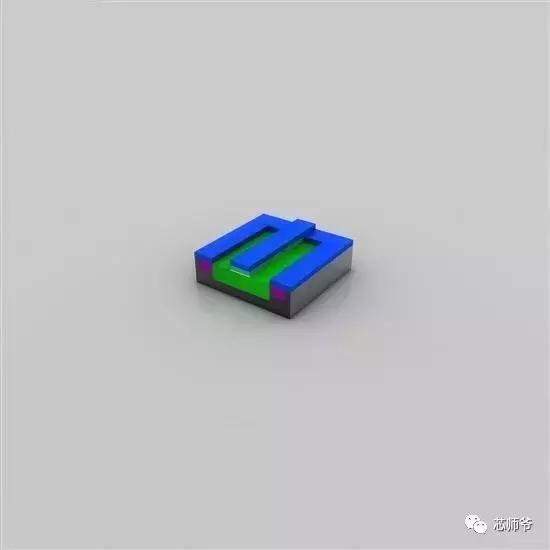

清除光刻胶:离子注入完成后,光刻胶也被清除,而注入区域(绿色部分)也已掺杂,注入了不同的原子。注意这时候的绿色和之前已经有所不同。

第五阶段合影

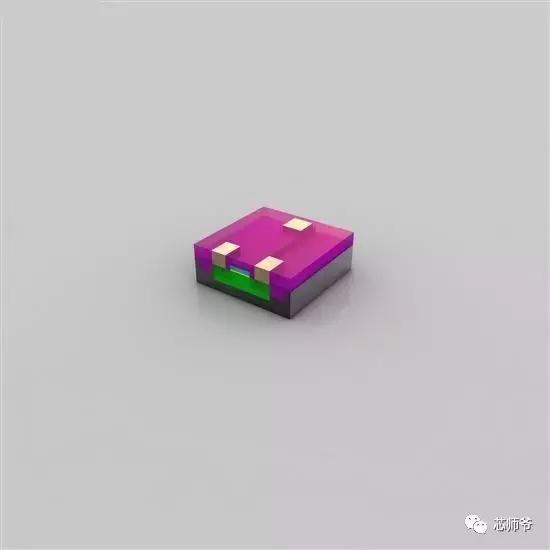

晶体管就绪:至此,晶体管已经基本完成。在绝缘材(品红色)上蚀刻出三个孔洞,并填充铜,以便和其它晶体管互连。

电镀:在晶圆上电镀一层硫酸铜,将铜离子沉淀到晶体管上。铜离子会从正极(阳极)走向负极(阴极)。

铜层:电镀完成后,铜离子沉积在晶圆表面,形成一个薄薄的铜层。

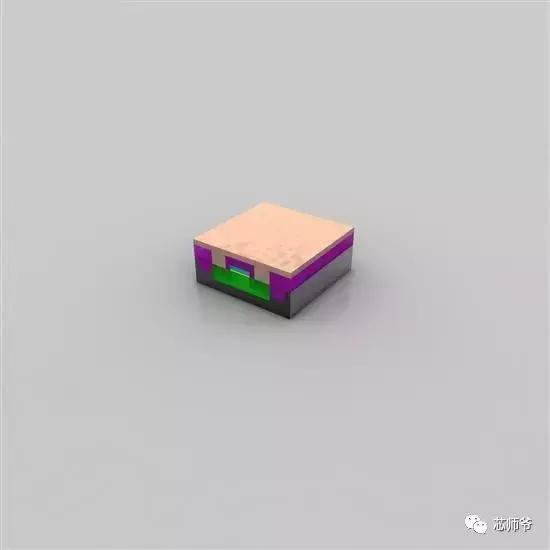

第六阶段合影

抛光:将多余的铜抛光掉,也就是磨光晶圆表面。

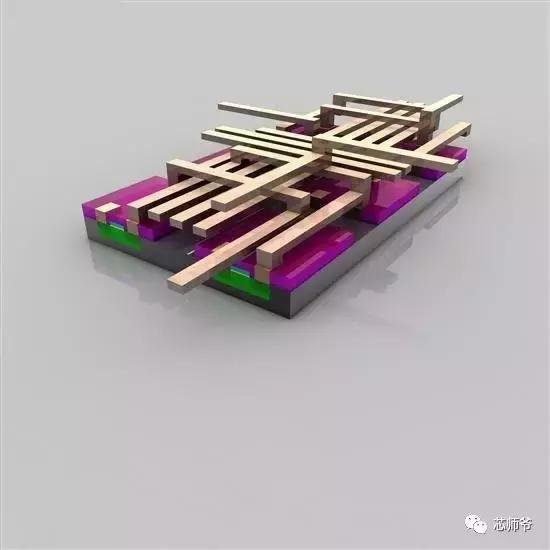

金属层:晶体管级别,六个晶体管的组合,大约500纳米。在不同晶体管之间形成复合互连金属层,具体布局取决于相应处理器所需要的不同功能性。芯片表面看起来异常平滑,但事实上可能包含20多层复杂的电路,放大之后可以看到极其复杂的电路网络,形如未来派的多层高速公路系统。

第七阶段合影

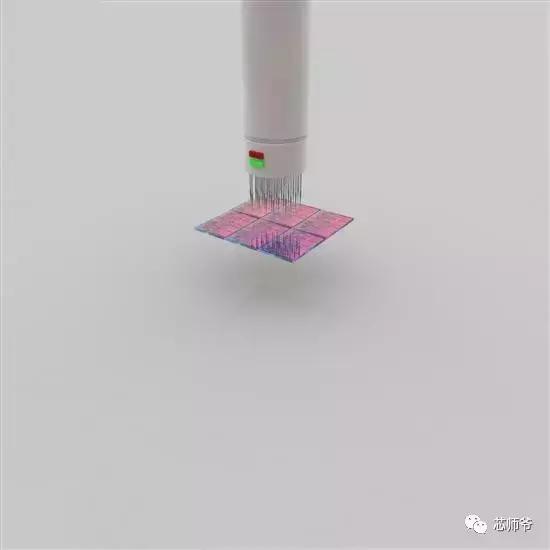

晶圆测试:内核级别,大约10毫米/0.5英寸。图中是晶圆的局部,正在接受第一次功能性测试,使用参考电路图案和每一块芯片进行对比。

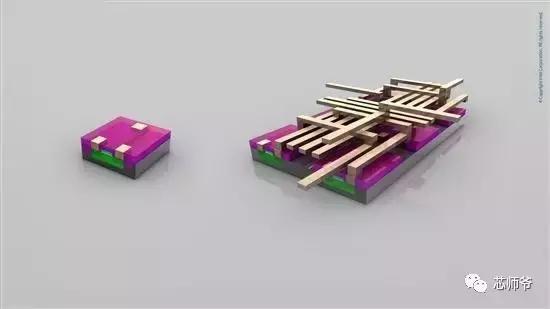

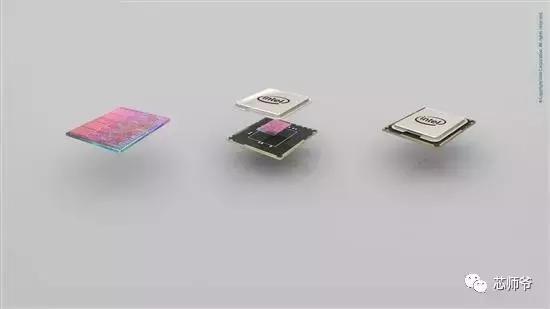

晶圆切片(Slicing):晶圆级别,300毫米/12英寸。将晶圆切割成块,每一块就是一个处理器的内核(Die)。

丢弃瑕疵内核:晶圆级别。测试过程中发现的有瑕疵的内核被抛弃,留下完好的准备进入下一步。

单个内核:内核级别。从晶圆上切割下来的单个内核,这里展示的是Core i7的核心。

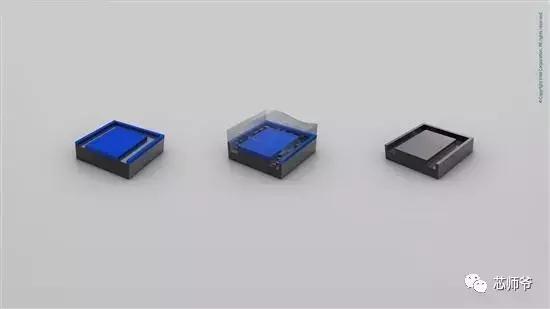

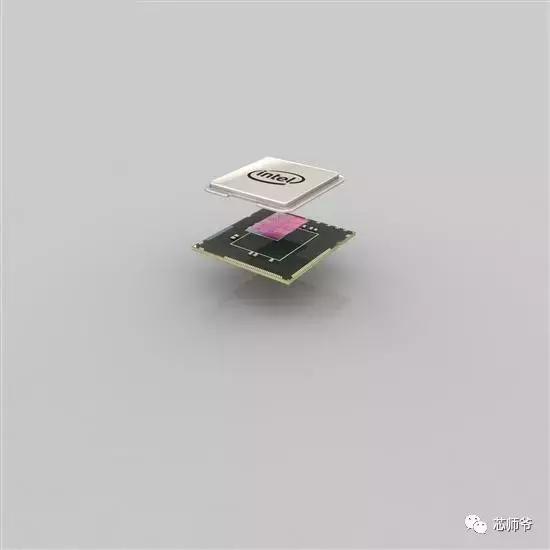

封装:封装级别,20毫米/1英寸。衬底(基片)、内核、散热片堆叠在一起,就形成了我们看到的处理器的样子。衬底(绿色)相当于一个底座,并为处理器内核提供电气与机械界面,便于与PC系统的其它部分交互。散热片(银色)就是负责内核散热的了。

处理器:至此就得到完整的处理器了(这里是一颗Core i7)。这种在世界上最干净的房间里制造出来的最复杂的产品实际上是经过数百个步骤得来的,这里只是展示了其中的一些关键步骤。

第九阶段合影

评论