“芯”潮澎湃 揭秘集成电路的“庐山真面目”

6、集成电路产业的分类

本文引用地址://m.amcfsurvey.com/article/201705/359846.htm集成电路产业依照不同的设计与生产性质,又可以分成专业代工厂(Foundry)、与整合组件制造商(IDM),分别有不同的产业技术能力与重要性,要了解集成电路产业的特性,就必须先了解集成电路产业的分类,以下分别讨论这两种不同厂商的特性。

专业代工厂(Foundry):制造商依照客户需求,为客户代工生产符合客户要求的产品,之后挂上客户的商标品牌,由客户自行销售。例如:台湾的台积电、联华电子、新加坡的特许、大陆的中芯等半导体公司。一般IC设计公司会下单给专业工代厂,是基于节省生产成本和部份管销费用成本为主要考虑,特别是集成电路(IC)的圆晶厂,投资金额动辄上百亿,并非一般的IC设计公司可以负担得起,因此交由专业代工厂可以节省许多制造研发的成本,转而进行设计研发的工作。

整合组件制造商(IDM:Integrated Device Manufacturer):制造商从设计、制造、测试、封装到销售自有品牌产品都一手包办的垂直整合型公司,通常都是国外大厂,例如:德州仪器(Texas Instruments)、英特尔(Intel)、摩托罗拉Motorola、三星Samsung、日本电子NEC、东芝Toshiba等公司。

值得注意的是,最早拥有晶圆厂的正是这些国际级的IDM大厂,台积电是全球第一家晶圆代工厂,早期并没有所谓的IC设计产业,因为IC设计公司就算画好设计图也找不到晶圆厂替他们代工生产,直到台积电成立以后,将晶圆制造变成一个独立的产业,称为晶圆代工厂,才造就了许多成功的IC设计公司。

IDM与Foundry哪个比较有优势?

2000年以前由于计算机、网络、多媒体(例如DVD)、无线通讯(例如2G)的快速发展,全球集成电路产品持续成长而供不应求,造成晶圆代工厂产能满载,IC设计公司的产品上市常常受制于晶圆厂,产品制作常常费时一年以上,不幸的是集成电路的产品生命周期很短,等一年以后产品才能上市,可能已经过时而要被淘汰了。所以有些规模较小设计公司也尝试自建晶圆厂,所以景气好的时候,有晶圆厂的IC设计公司可以掌握自己的产品,不过份依赖晶圆代工厂,如果产能被别人掌握,只要分不到产能,产品就不能准时上市,因此自建晶圆厂不失为一个好方法。

但是2000年以后,网络泡沫化,全球集成电路产品需求持续下滑而供过于求,造成晶圆代工厂产能闲置,以往IC设计公司的产品受制于晶圆厂的现象已经不存在,因此自建晶圆厂的必要性并不大,而且一但加入了IC制造产业,则每年必须支出庞大的制造研发成本,这笔费用动辄数百亿,会严重影响IC设计研发的支出而使公司顾此失彼,2004年台湾矽统科技将晶圆厂卖给联华电子公司,同样的,超微半导体(AMD)当初也做出了重要决定,将晶圆厂剥离与中东土豪合资成立专业代工厂格罗方德半导体(GLOBALFOUNDRIES)。因此,IC设计公司自建晶圆厂有利有弊,必须衡量公司的财务状况,以及公司未来的营运规划,才能做出最合适的决定,因此,未来IC产业的趋势就是分工与降低风险,晶圆代工集中化会越来越明显,除非有品牌或是广阔的出海口,否则整合组件制造商(IDM)将越来越少。

7、闸极线宽长度为什么重要?

40nm,28nm,10nm,7nm到3纳米,何时才是极限?

数字集成电路设计的最底层为晶体管,也就是组成集成电路的最小单位,晶体管的种类很多,目前在数字集成电路中均是使用CMOS,一个数字集成电路上可能含有数百万个CMOS,「晶体管(CMOS)」就好像生物体中的「细胞」一样。要了解闸极线宽的重要性,我们先来了解下 MOSFET。

什么是MOSFET?

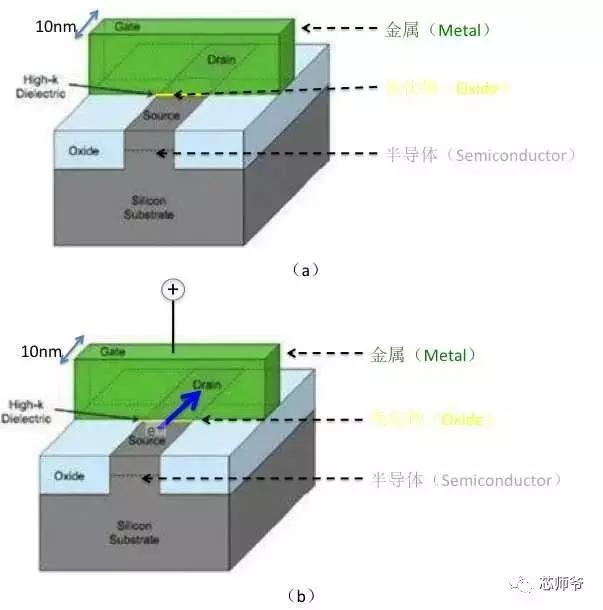

MOSFET 的全名是“金属-氧化物-半导体场效电晶体(Metal Oxide Semiconductor Field Effect Transistor,MOSFET)”,前面灰色的区域(硅)叫做“源极(Source)”,后面灰色的区域(硅)叫做“汲极(Drain)”,中间有块金属(绿色)突出来叫做“闸极(Gate)”,闸极下方有一层厚度很薄的氧化物(黄色),中间由上而下依序为金属(Metal)、氧化物(Oxide)、半导体(Semiconductor)。

MOSFET 的工作原理与用途

MOSFET 的工作原理很简单,电子由左边的源极流入,经过闸极下方的电子通道,由右边的汲极流出,中间的闸极则可以决定是否让电子由下方通过,有点像是水闸的开关一样,因此称为“闸”;电子是由源极流入,也就是电子的来源,因此称为“源”;电子是由汲极流出,:汲者,引水于井也,也就是由这里取出电子,因此称为“汲”。

▲MOSFET工作原理

当闸极不加电压,电子无法导通,代表这个位是 0,当闸极加正电压,电子可以导通,代表这个位是 1,CMOS晶体管的工作原理为在闸极施予一固定电压,使通道形成,电流即可通过。在数位电路中,藉由电流通过与否,便可代表逻辑的1或0。

MOSFET 是目前半导体产业最常使用的一种场效电晶体(FET),科学家将它制作在硅晶圆上,是数位讯号的最小单位,一个 MOSFET 代表一个 0 或一个 1,就是电脑里的一个“位(bit)”。电脑是以 0 与 1 两种数码讯号来运算;在硅芯片上有数十亿个 MOSFET,就代表数十亿个 0 与 1,再用金属导线将这数十亿个 MOSFET 的源极、汲极、闸极链接起来,电子讯号在这数十亿个 0 与 1 之间流通就可以交互运算,最后得到使用者想要的加、减、乘、除运算结果,这就是计算机的基本工作原理。晶圆厂像台积电、联电与中芯,就是在硅晶圆上制作数十亿个 MOSFET 的工厂。

闸极线宽:半导体制程进步的关键

在 MOSFET 中,“闸极线宽长度(Gate length)”大约 10 纳米,是所有构造中最细小也最难制作的,因此我们常常以闸极长度来代表半导体制程的进步程度,这就是所谓的“制程线宽”。闸极线宽长度会随制程技术的进步而变小,从早期的 0.18 微米、0.13 微米,进步到 90 纳米、65 纳米、45 纳米、28 纳米,到目前最新制程 10 纳米。当闸极线宽长度愈小,则整个 MOSFET 就愈小,而同样含有数十亿个 MOSFET 的芯片就愈小,封装以后的集成电路就愈小,最后做出来的手机就愈小!10 纳米到底有多小呢?细菌大约 1 微米,病毒大约 100 纳米,换句话说,人类现在的制程技术可以制作出只有病毒 1/10(10 纳米)的结构,是不是有点无法想象?

▲台积电未来技术路线进度表

线宽越窄所遇到的瓶颈与解决的方法

集成电路在线宽小于28nm的时候,有两个非常重要的制程技术HKMG与FinFET:

HKMG(高介电常数金属闸极High K Metal Gate,K is permittivity or dielectric constant )

外加电场于两个平行金属板,中间如果放入绝缘材料,材料内部也会形成电场,外电场与内部电场的比值,称为介电常数,两个金属板极化电荷越多,抵消外电场能力越强,内电场越小,介电常数就越大,同样的电容就越大。

介电常数是衡量一个介质束缚电荷的能力,也可表征材料的绝缘性能,介电常数越大,束缚电荷的能力越强,材料的绝缘性能越好,其定义就是材料介电常数越高说明电极化越强,外电场削弱越厉害。当然在电极化无穷大的情况,实际上电子就自由了,此时外场被完全抵消,也就是电屏蔽,此时介电常数正无穷大,材料实际上就是导体了,所以这也是为什么在电梯里面手机收不到电磁波讯号的原因。

为什么要用高介电常数的材料?半导体前段制程的挑战,不外乎是不断微缩闸极线宽,在固定的单位面积之下增加电晶体数目,半导体制程一直在挑战极限,随着闸极线宽缩小,氧化层厚度跟着缩减,导致绝缘效果降低,使得漏电流成为令业界困扰不已的副作用,利用高介电常数材料来增加电容值,就可以达到降低漏电流的目的,半导体制造业者在28纳米制程节点导入的高介电常数金属闸极(High-kMetalGate,HKMG),即是利用高介电常数材料来增加电容值,以达到降低漏电流的目的。

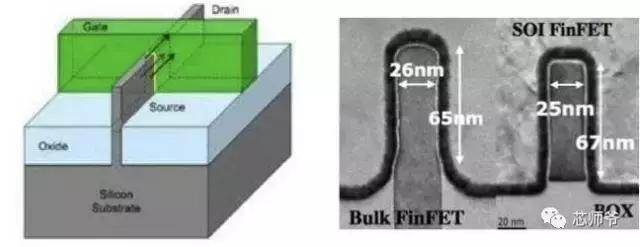

FinFET(鳍式场效电晶体Fin Field Effect Transistor,FinFET)

根据增加氧化物绝缘层电容达到在线宽缩小之后减低漏电的理论,增加绝缘层的表面积亦是一种改善漏电流现象的方法。鳍式场效电晶体(Fin Field Effect Transistor,FinFET)即是藉由增加绝缘层的表面积来增加电容值,降低漏电流以达到降低功耗的目的,FinFET将过去的平面式结构转为立体式结构,增加对闸极的控制能力,这项技术据说可以将摩尔定律延长到2022年。

▲FinFET技术结构示意图与TEM显微镜截面图

评论